इंटीग्रेशन चुनौती का परिचय 💡

सिस्टम इंजीनियरिंग आंतरिक रूप से जटिल है। अवधारणात्मक मॉडल से भौतिक हार्डवेयर में जाने पर, त्रुटि की अनुमति बहुत कम हो जाती है। प्रोजेक्ट अक्सर फेल होने वाले सबसे महत्वपूर्ण क्षेत्रों में से एक आवश्यकता ट्रेसेबिलिटी है। यह केस स्टडी एक वास्तविक दुनिया के परिदृश्य का विश्लेषण करती है जहां एक हार्डवेयर इंटीग्रेशन प्रयास विफल हो गया, तकनीकी कौशल की कमी के कारण नहीं, बल्कि एक सिस्टम मॉडलिंग भाषा (SysML) ढांचे के भीतर आवश्यकताओं को सिस्टम व्यवहार से जोड़ने के तरीके में विफलता के कारण। लक्ष्य विफलता के बिंदुओं को विश्लेषित करना, तकनीकी प्रभावों को समझना और यह बताना है कि कठोर मॉडलिंग कैसे इस तरह के परिणामों को रोक सकती है।

ट्रेसेबिलिटी केवल एक चेकलिस्ट आइटम से अधिक है। यह सिस्टम अखंडता की रीढ़ है। जब एक आवश्यकता डिज़ाइन तत्व से जुड़ी नहीं होती है, तो उस तत्व के वास्तव में इरादे को पूरा करने की जांच करने का कोई तरीका नहीं होता है। उच्च जोखिम वाले वातावरणों, जैसे एयरोस्पेस या स्वचालित वाहन विकास में, ऐसी असंगति के कारण लागत वाले पुनर्निर्माण, शेड्यूल देरी और सुरक्षा जोखिम हो सकते हैं। इस विश्लेषण में विफलता के तकनीकी तत्वों और उन विशिष्ट SysML निर्माणों पर ध्यान केंद्रित किया गया है जिनका कम या गलत उपयोग किया गया था।

प्रोजेक्ट पृष्ठभूमि और दायरा 📦

जिस प्रोजेक्ट की बात की जा रही है, उसमें स्वचालित नेविगेशन प्लेटफॉर्म के लिए बहु-सेंसर फ्यूजन इकाई के विकास का काम शामिल था। सिस्टम में LIDAR, रडार और ऑप्टिकल कैमरों को एकीकृत प्रोसेसिंग नोड में एकीकृत करने की आवश्यकता थी। विकास चक्र मॉडल-आधारित सिस्टम इंजीनियरिंग (MBSE) दृष्टिकोण का पालन करता था, जिसमें संरचना और आवश्यकताओं को परिभाषित करने के लिए SysML का उपयोग किया गया था।

प्रमुख प्रोजेक्ट पैरामीटर:

- प्रणाली प्रकार:स्वचालित नेविगेशन सेंसर सूट

- विकास चरण:सिस्टम इंटीग्रेशन और सत्यापन

- प्राथमिक तकनीक:मॉडलिंग और विशिष्टता के लिए SysML

- परिणाम:अपरीक्षित आवश्यकता अंतर के कारण इंटीग्रेशन विफलता

टीम ने प्रारंभिक चरणों में एक व्यापक सेट आवश्यकताओं का निर्माण किया। हालांकि, इन टेक्स्टुअल आवश्यकताओं और भौतिक डिज़ाइन ब्लॉक्स के बीच संबंध असंगत था। जबकि प्रारंभिक सिस्टम संरचना का मॉडल बनाया गया था, विस्तृत इंटीग्रेशन चरण में ट्रेसेबिलिटी श्रृंखलाओं में आवश्यक कठोरता की कमी थी। यह असंगति केवल तब सामने आई जब पहले भौतिक प्रोटोटाइप एकीकृत किए गए।

आधुनिक सिस्टम इंजीनियरिंग में SysML की भूमिका 🧩

SysML सिस्टम संरचनाओं, व्यवहारों और आवश्यकताओं का वर्णन करने का मानकीकृत तरीका प्रदान करता है। एक अच्छी तरह से संरचित मॉडल में, प्रत्येक आवश्यकता को विभाजित, आवंटित और सत्यापित किया जाना चाहिए। भाषा कई डायग्राम प्रकारों का समर्थन करती है, जिनमें शामिल हैं:

- आवश्यकता डायग्राम: सिस्टम के “क्या” को परिभाषित करते हैं।

- ब्लॉक परिभाषा डायग्राम (BDD): सिस्टम की “संरचना” को परिभाषित करते हैं।

- आंतरिक ब्लॉक डायग्राम (IBD): ब्लॉक्स के बीच “इंटरफेस” और संबंधों को परिभाषित करते हैं।

- पैरामेट्रिक डायग्राम: “सीमाओं” और गणितीय संबंधों को परिभाषित करते हैं।

विश्लेषण किए जा रहे परिदृश्य में, आवश्यकता डायग्राम को व्यापक रूप से भरा गया था। टीम ने कार्यात्मक और गैर-कार्यात्मक आवश्यकताओं को सफलतापूर्वक दर्ज कर लिया था। हालांकि, इन आवश्यकताओं को BDD और IBD में विशिष्ट ब्लॉक्स में आवंटित करने की प्रक्रिया ढीली थी। कई आवश्यकताएं अनाथ छोड़ दी गईं, जिसका अर्थ था कि वे मॉडल में मौजूद थीं लेकिन डिज़ाइन तत्वों के साथ कोई आउटगोइंग संबंध नहीं था। इससे एक गलत पूर्णता की भावना उत्पन्न हुई। मॉडल भरा हुआ लगता था, लेकिन सत्यापन की तार्किक प्रवाह टूट गया था।

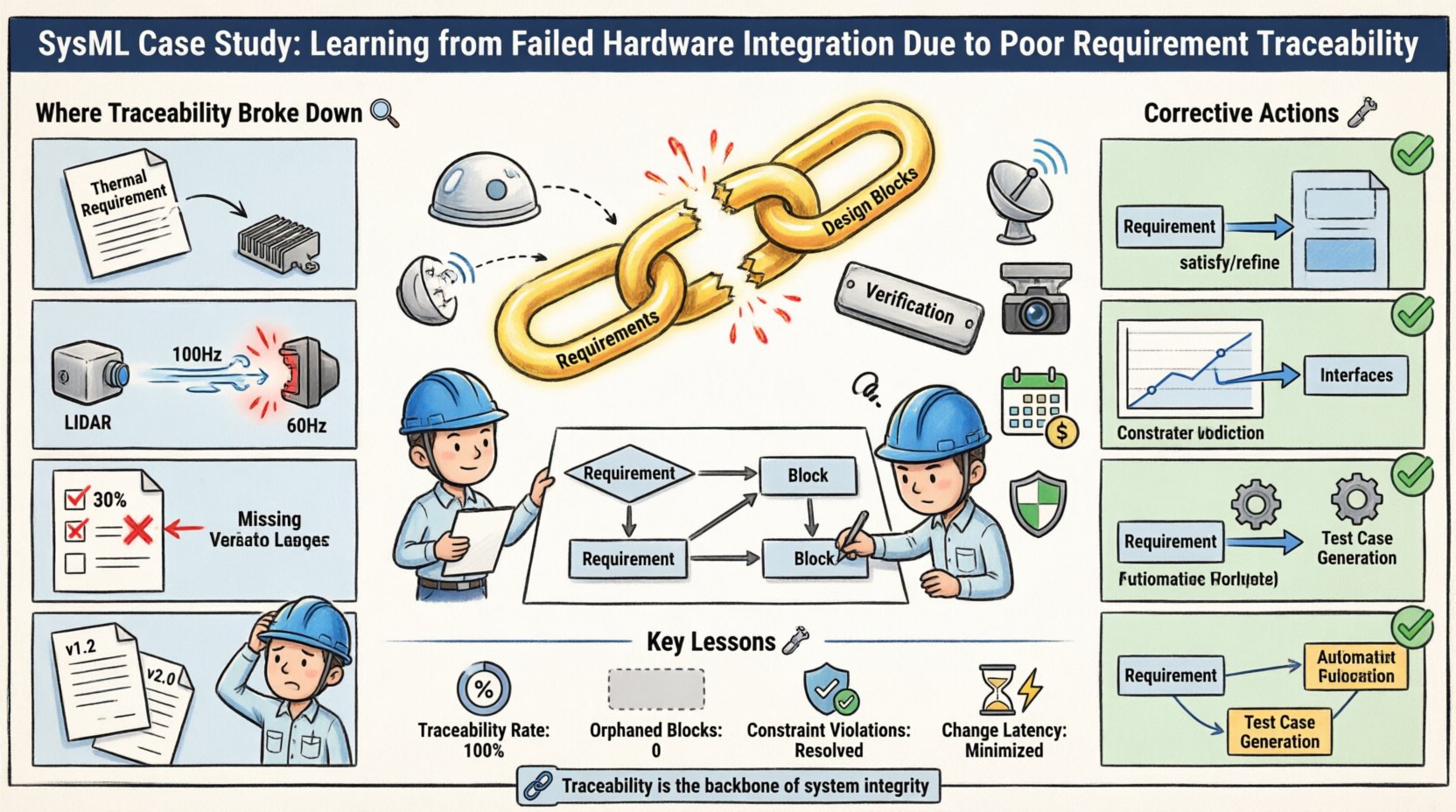

जहां ट्रेसेबिलिटी टूट गई 🔍

विफलता एक घटना नहीं थी, बल्कि समय के साथ जमा होने वाली छोटी-छोटी लापरवाहियों का एक श्रृंखला थी। निम्नलिखित बिंदु बताते हैं कि मॉडलिंग प्रक्रिया के दौरान ट्रेसेबिलिटी श्रृंखलाएं कहां टूटीं।

1. असंगत आवश्यकता आवंटन

आवश्यकता विश्लेषण चरण के दौरान, � ingineers ने आवश्यकताओं को उच्च-स्तरीय सिस्टम ब्लॉक्स में आवंटित किया। जैसे-जैसे डिज़ाइन उप-प्रणालियों में आगे बढ़ा, इन आवंटनों को नीचे तक नहीं फैलाया गया। उदाहरण के लिए, एक तापीय प्रबंधन आवश्यकता को “सेंसर इकाई” ब्लॉक में आवंटित किया गया लेकिन आंतरिक ब्लॉक आरेख में विशिष्ट “हीट सिंक” घटक से कभी भी जोड़ा नहीं गया। जब हार्डवेयर का निर्माण किया गया, तो हीट सिंक छोटा था क्योंकि तापीय आवश्यकता डिज़ाइन अनियमिताओं को सक्रिय रूप से प्रभावित नहीं कर रही थी।

2. इंटरफेस परिभाषा के अंतराल

आंतरिक ब्लॉक आरेख घटकों के बीच पोर्ट और कनेक्टरों को परिभाषित करते हैं। इस मामले में, डेटा प्रवाह इंटरफेस को मॉडल किया गया था, लेकिन सिग्नल समय सीमाओं को इंटरफेस पोर्ट से जोड़ा नहीं गया था। LIDAR डेटा स्ट्रीम को 100Hz पर चलने की अपेक्षा थी, लेकिन इस आवश्यकता को संचार इंटरफेस पोर्ट से जोड़ा नहीं गया था। परिणामस्वरूप, इंटरफेस कंट्रोलर को 60Hz के लिए डिज़ाइन किया गया था, जिससे एकीकरण के दौरान डेटा का नुकसान हुआ।

3. सत्यापन लिंक अनुपस्थित

एक मजबूत मॉडल के लिए सत्यापन लिंक की आवश्यकता होती है। यह एक आवश्यकता को एक परीक्षण मामले या एक विशिष्ट डिज़ाइन तत्व से जोड़ता है जो दिखाता है कि आवश्यकता पूरी की गई है। परियोजना टीम लगभग 30% आवश्यकताओं के लिए इन सत्यापन लिंक को बनाने के लिए उपेक्षा कर गई। इन लिंक के बिना, सत्यापन योजना बनाने का कोई स्वचालित तरीका नहीं था। परीक्षण चरण हाथ से और अनियमित रूप से हुआ, जिससे कवरेज के क्षेत्रों को छोड़ दिया गया।

4. संस्करण नियंत्रण और बेसलाइन विचलन

आवश्यकताएं परियोजना के दौरान विकसित हुईं। नए सेंसर प्रौद्योगिकियों को समायोजित करने के लिए बदलाव के अनुरोध किए गए। हालांकि, मॉडल ने आवश्यकता-ब्लॉक संबंधों पर सख्त संस्करण प्रबंधन को लागू नहीं किया। जब एक आवश्यकता में बदलाव हुआ, तो ऊपरी डिज़ाइन ब्लॉक्स को समीक्षा के लिए चिह्नित नहीं किया गया। इस विचलन का अर्थ यह था कि हार्डवेयर एक पुराने संस्करण के निर्देशानुसार बनाया गया, जो सिस्टम मॉडल में अब अद्यतन नहीं था।

मॉडलिंग स्थितियों की तुलना 📊

मॉडल की इच्छित स्थिति और वास्तविक स्थिति के बीच के अंतर को देखने के लिए, निम्नलिखित तुलना सारणी को देखें। यह विशिष्ट क्षेत्रों को उजागर करता है जहां ट्रेसेबिलिटी कमजोर थी।

| ट्रेसेबिलिटी पहलू | इच्छित स्थिति (आदर्श) | वास्तविक स्थिति (अवलोकित) | परिणामस्वरूप समस्या |

|---|---|---|---|

| आवश्यकता आवंटन | आवश्यकताओं का 100% डिज़ाइन ब्लॉक्स से जुड़ा | आवश्यकताओं का 70% डिज़ाइन ब्लॉक्स से जुड़ा | अपरीक्षित डिज़ाइन निर्णय |

| इंटरफेस सीमाएं | सिग्नल समय सीमाएं पोर्ट गुणों से जुड़ी | केवल पाठ में समय सीमाएं | इंटरफेस असंगति (60Hz बनाम 100Hz) |

| सत्यापन लिंक | परीक्षण मामलों से सीधा लिंक | हाथ से ट्रेसेबिलिटी मैट्रिक्स | छूटी परीक्षण कवरेज |

| बदलाव प्रबंधन | बदलाव पर स्वचालित प्रभाव विश्लेषण | हाथ से समीक्षा की आवश्यकता | पुराने हार्डवेयर निर्माण |

विस्तृत प्रभाव विश्लेषण 📉

खराब ट्रेसेबिलिटी के परिणाम तुरंत और मापने योग्य थे। चार सप्ताह के लिए योजना बनाई गई एकीकरण चरण बारह सप्ताह तक बढ़ गया। मूल कारण विश्लेषण ने यह पता लगाया कि मॉडलिंग चरण के दौरान भूल जाने वाली मूल आवश्यकताओं को पूरा करने के लिए हार्डवेयर को फिर से डिज़ाइन करना पड़ा।

लागत प्रभाव

सेंसर हाउसिंग और संचार इंटरफेस बोर्ड के पुनर्डिज़ाइन करने में महत्वपूर्ण सामग्री और श्रम लागत आई। नए घटकों की खरीदारी त्वरित शिपिंग के कारण मूल्य में वृद्धि के कारण हुई। बजट के अतिरिक्त होने का सीधा कारण अनलिंक्ड आवश्यकताओं को ठीक करने के लिए किए गए पुनर्कार्य के कारण था।

समय सीमा में देरी

एकीकरण परीक्षण तब तक आगे नहीं बढ़ सका जब तक हार्डवेयर विनिर्माण निर्देशों के अनुरूप नहीं हो गया। देरी ने सॉफ्टवेयर एकीकरण चरण को पीछे धकेल दिया। चूंकि सॉफ्टवेयर हार्डवेयर सिग्नल पर निर्भर था, पूरे सिस्टम मान्यता समयरेखा को संकुचित कर दिया गया। इसने टीम को लॉन्च तिथि को पूरा करने के लिए ओवरटाइम काम करने के लिए मजबूर कर दिया, जिससे नए त्रुटियों के आने का जोखिम बढ़ गया।

सुरक्षा जोखिम

सबसे महत्वपूर्ण प्रभाव सुरक्षा से जुड़ा था। थर्मल प्रबंधन के असफल होने का मतलब था कि सेंसर उच्च वातावरणीय तापमान की स्थिति में ओवरहीट हो सकते थे। इसे प्रारंभिक परीक्षण के दौरान नहीं पकड़ा गया क्योंकि मॉडल में थर्मल आवश्यकता को सक्रिय रूप से निगरानी में नहीं रखा गया था। उत्पादन परिवेश में, इसके संचालन के दौरान सिस्टम विफलता के कारण हो सकता था, जिससे कर्मचारियों और संपत्ति को खतरा होता।

सुधारात्मक कार्रवाई और SysML सुधार 🛠️

जब विफलता का पता चला, तो इंजीनियरिंग टीम ने SysML मॉडल के भीतर ट्रेसेबिलिटी श्रृंखलाओं को मजबूत करने पर ध्यान केंद्रित करके एक सुधारात्मक रणनीति लागू की। सिस्टम परिभाषा की अखंडता को बहाल करने के लिए निम्नलिखित चरण अपनाए गए।

1. आवंटन नियमों को बलपूर्वक लागू किया गया

टीम ने एक नियम स्थापित किया कि कोई भी आवश्यकता डिज़ाइन ब्लॉक में वैध आवंटन के बिना अगले विकास चरण में नहीं ले जाई जा सकती है। इसे मॉडल सत्यापन स्क्रिप्ट के माध्यम से लागू किया गया। यदि कोई आवश्यकता कोई बाहरी “संतुष्ट करना” या “सुधारना” संबंध नहीं रखती थी, तो मॉडल उसे अपूर्ण चिह्नित कर देता था। इससे इंजीनियरों को हर आवश्यकता को एक भौतिक या तार्किक घटक से जोड़ने के लिए मजबूर किया गया।

2. इंटरफेस सीमा समावेश

सिग्नल समय और डेटा दर की आवश्यकताओं को पाठ दस्तावेजों से पैरामेट्रिक आरेखों में स्थानांतरित कर दिया गया। इन आरेखों में अब इंटरफेस पोर्ट के गुणों को स्पष्ट रूप से सीमित किया जाता है। इससे यह सुनिश्चित होता है कि यदि कोई आवश्यकता बदलती है, तो इंटरफेस सीमाएं स्वचालित रूप से अपडेट हो जाती हैं, जिससे डिज़ाइन टीम को सूचना भेजी जाती है।

3. स्वचालित सत्यापन योजना

टीम ने एक कार्यप्रवाह लागू किया जहां सत्यापन लिंक स्वचालित रूप से परीक्षण मामले उत्पन्न करते हैं। प्रत्येक आवश्यकता जिसमें सत्यापन लिंक है, गुणवत्ता प्रबंधन प्रणाली में एक रुके हुए परीक्षण आइटम बनाती है। इससे यह सुनिश्चित होता है कि कोई भी आवश्यकता बिना संबंधित परीक्षण योजना के सत्यापित नहीं की जाती है। इससे परीक्षण कवरेज के ट्रैकिंग में मानवीय त्रुटि का जोखिम कम हो जाता है।

4. परिवर्तन प्रभाव विश्लेषण

जब कोई आवश्यकता में संशोधन किया गया, तो मॉडल को पूछताछ करके सभी नीचे की ओर निर्भरताओं को खोजा गया। जिस ब्लॉक ने उस आवश्यकता को संतुष्ट किया या सुधारा, उसे उजागर कर दिया गया। इस दृश्य प्रतिक्रिया ने टीम को यह देखने में सक्षम बनाया कि बदलाव को लागू करने से पहले कौन से हार्डवेयर घटकों को पुनर्मूल्यांकन करने की आवश्यकता है।

भविष्य के प्रोजेक्ट्स के लिए सीखें 🚀

यह केस स्टडी MBSE को अपनाने वाली सिस्टम इंजीनियरिंग टीमों के लिए कई महत्वपूर्ण सीख देती है। मुख्य सीख यह है कि मॉडल केवल उन लिंक्स के अनुसार ही अच्छा होता है जो इसमें होते हैं। अलग-अलग तत्वों से भरा मॉडल एकीकरण के दौरान कोई मूल्य नहीं देता है।

- ट्रेसेबिलिटी एक निरंतर प्रक्रिया है: यह एक चरण के अंत में पूरा करने वाला कार्य नहीं है। आवश्यकताओं के विकास के साथ-साथ ट्रेसेबिलिटी को पूरे जीवनचक्र में बनाए रखना आवश्यक है।

- लिंक डिज़ाइन को आगे बढ़ाते हैं: डिज़ाइन तत्वों के निर्माण को आवश्यकताओं के द्वारा ही आगे बढ़ाना चाहिए, न कि इसके विपरीत। यदि कोई डिज़ाइन तत्व बिना आवश्यकता के मौजूद है, तो तकनीकी रूप से यह तकनीकी ऋण है।

- मान्यता एक महत्वपूर्ण बात है: सत्यापन लिंक को जल्दी से स्थापित करना आवश्यक है। हार्डवेयर बनने के बाद आवश्यकताओं को सत्यापित करने का इंतजार करना बहुत देर हो चुकी है।

- उपकरण समर्थन: यद्यपि सॉफ्टवेयर उपकरणों का विशेष रूप से उल्लेख नहीं किया गया है, लेकिन संबंधों को पूछताछ करने और निर्भरताओं को दृश्याकृत करने की क्षमता आवश्यक है। मैन्युअल ट्रैकिंग में त्रुटि का खतरा रहता है।

टिकाऊ ट्रेसेबिलिटी श्रृंखलाओं को लागू करना 🔗

दोहराव को रोकने के लिए, निम्नलिखित चेकलिस्ट को हार्डवेयर निर्माण में जाने से पहले सभी SysML मॉडल पर लागू किया जाना चाहिए।

एकीकरण से पहले चेकलिस्ट

- आवश्यकता ढांचा: क्या सभी आवश्यकताओं को कम से कम एक ब्लॉक में आवंटित किया गया है?

- इंटरफेस पूर्णता: क्या सभी भौतिक इंटरफेस के लिए परिभाषित डेटा प्रकार और समय सीमा सीमाएं हैं?

- प्रतिबंध वैधता: क्या वर्तमान डिजाइन मानों द्वारा पैरामेट्रिक प्रतिबंध पूरे किए जाते हैं?

- सत्यापन लिंक: क्या प्रत्येक आवश्यकता के लिए एक परीक्षण मामले या सत्यापन विधि तक पथ है?

- परिवर्तन इतिहास: क्या मॉडल का संस्करण हार्डवेयर विवरणों के संस्करण के साथ समकालीन है?

मॉनिटरिंग मापदंड

टीमों को ट्रेसेबिलिटी के स्वास्थ्य को सुनिश्चित करने के लिए विशिष्ट मापदंडों को ट्रैक करना चाहिए। इन मापदंडों को मॉडल रिपॉजिटरी से निकाला जा सकता है।

- ट्रेसेबिलिटी दर: मान्य लिंक वाली आवश्यकताओं का प्रतिशत।

- अनाथ ब्लॉक: बिना संबंधित आवश्यकताओं वाले डिजाइन ब्लॉकों की संख्या।

- प्रतिबंध उल्लंघन: वर्तमान में उल्लंघित पैरामेट्रिक प्रतिबंधों की संख्या।

- परिवर्तन लेटेंसी: आवश्यकता परिवर्तन और मॉडल अद्यतन के बीच लंबी अवधि।

मॉडल-आधारित सिस्टम इंजीनियरिंग पर अंतिम विचार 🏁

इस केस स्टडी में वर्णित विफलता सिस्टम इंजीनियरिंग में अनुशासन के महत्व के लिए एक स्पष्ट याद दिलाती है। SysML एक शक्तिशाली उपकरण है जो स्पष्टता और ठोसता की अनुमति देता है, लेकिन इसके सक्रिय प्रबंधन की आवश्यकता होती है। तकनीक स्वयं अच्छी प्रथाओं को लागू नहीं करती है; इंजीनियरों को उन्हें परिभाषित और लागू करना होता है।

मॉडल को एकमात्र सच्चाई के स्रोत के रूप में मानते हुए और यह सुनिश्चित करते हुए कि प्रत्येक कोड लाइन और सर्किट बोर्ड पर प्रत्येक घटक को एक विशिष्ट आवश्यकता तक ट्रेस किया जा सके, संगठन एकीकरण विफलता के जोखिम को कम कर सकते हैं। सफल हार्डवेयर एकीकरण का रास्ता स्पष्ट, अटूट ट्रेसेबिलिटी कड़ियों से बना होता है। जब इन कड़ियों को तोड़ा जाता है, तो भौतिक प्रणाली पीड़ित होती है। जब वे मजबूत होती हैं, तो प्रणाली दृढ़, विश्वसनीय और उसके मूल उद्देश्य के अनुरूप होती है।

भविष्य के प्रोजेक्ट्स को ट्रेसेबिलिटी के आसपास प्रशिक्षण और प्रक्रिया परिभाषा में निवेश करना चाहिए। इसमें एक मान्य लिंक क्या है, इसकी परिभाषा और मॉडल परिवर्तनों के आसपास शासन की स्थापना शामिल है। रोकथाम की लागत हमेशा सुधार की लागत से कम होती है। जटिल हार्डवेयर एकीकरण के संदर्भ में, सफलता और विफलता के बीच का अंतर अक्सर मॉडल में आवश्यकताओं के जुड़ने के विवरण में होता है।