मॉडल-आधारित सिस्टम इंजीनियरिंग (MBSE) ने जटिल प्रणालियों के डिज़ाइन, विश्लेषण और सत्यापन के तरीके को बदल दिया है। दस्तावेज़-केंद्रित प्रक्रियाओं से मॉडल-केंद्रित कार्यप्रणालियों में स्थानांतरण करके, संगठनों को प्रणाली वार्कप्लान के लिए एकमात्र सत्य स्रोत मिलता है। हालांकि, सिस्टम मॉडलिंग भाषा (SysML) में स्थानांतरण के साथ विशिष्ट तकनीकी चुनौतियाँ उत्पन्न होती हैं। बहुत से इंजीनियरिंग टीमें सत्यापन विफलताओं का सामना करती हैं, जिससे प्रगति रुक जाती है, ट्रेसेबिलिटी धुंधली हो जाती है और प्रणाली की अखंडता को नुकसान पहुँचता है।

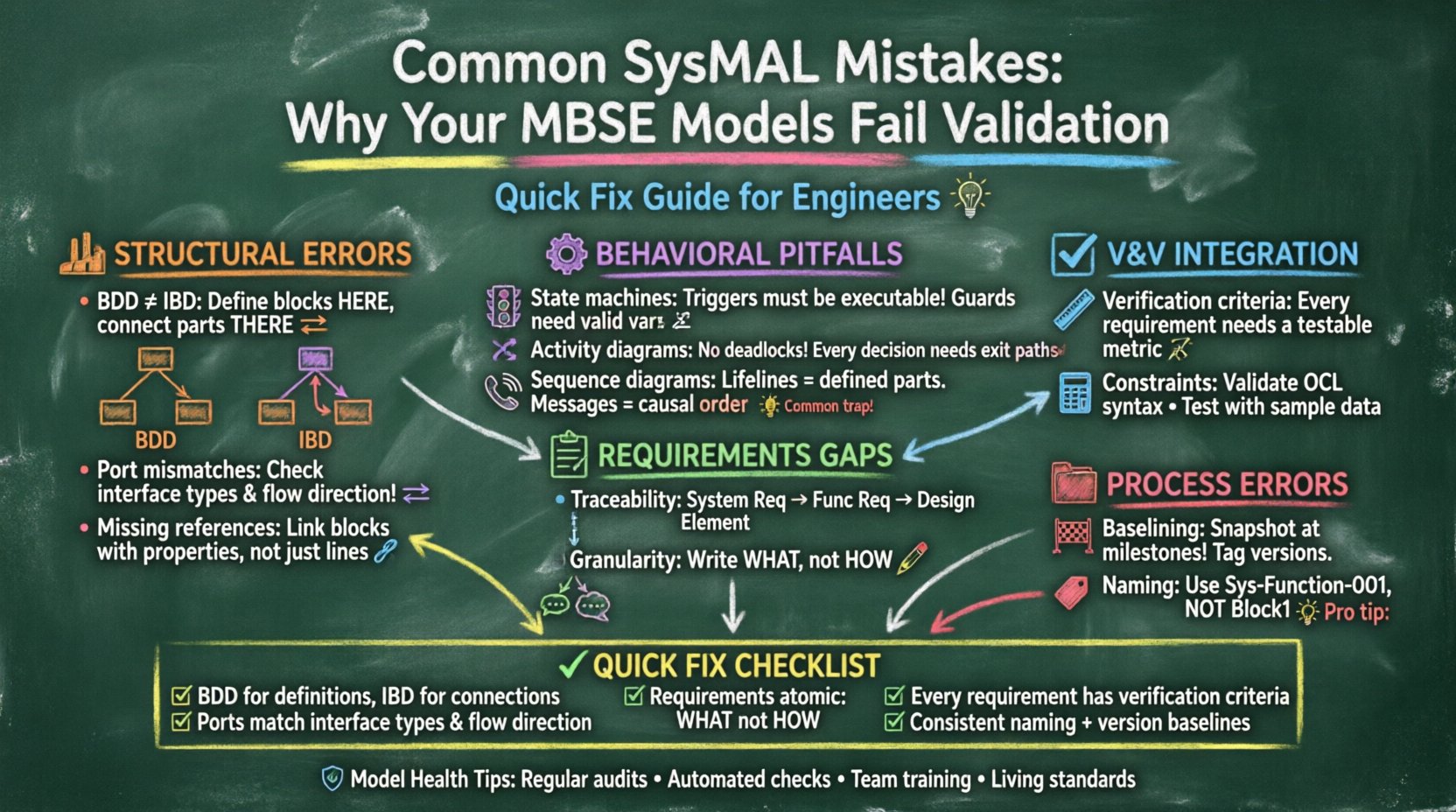

जब कोई SysML मॉडल सत्यापन में विफल होता है, तो यह केवल व्याकरणिक त्रुटि नहीं होती है; यह अक्सर ब्लॉक परिभाषा, व्यवहार धाराओं या आवश्यकता आवंटन के संबंध में गहन अवधारणात्मक गलतफहमी का लक्षण होती है। इन त्रुटियाँ इंजीनियरिंग जीवनचक्र के माध्यम से फैलती हैं, जिसके कारण एकीकरण या परीक्षण चरणों में महंगी पुनर्कार्य की आवश्यकता होती है। यह मार्गदर्शिका SysML मॉडलिंग में सबसे आम गलतियों का विवरण देती है और मॉडल की स्वास्थ्य और सत्यापन सुसंगतता सुनिश्चित करने के लिए वास्तविक सुधारात्मक कार्रवाई प्रदान करती है।

1. संरचनात्मक मॉडलिंग की गलतियाँ 🏗️

किसी भी SysML मॉडल का आधार उसकी संरचनात्मक परिभाषाओं में होता है। यहाँ की त्रुटियाँ बाहर की ओर फैलती हैं, जिससे व्यवहार और आवश्यकताओं को प्रभावित करती हैं। एक मजबूत संरचना सुनिश्चित करती है कि भाग, पोर्ट और संबंधों को तार्किक रूप से परिभाषित किया गया हो।

1.1 ब्लॉक परिभाषा आरेख (BDD) और आंतरिक ब्लॉक आरेख (IBD) को गलती से एक जैसा मानना 📐

सबसे व्यापक गलतियों में से एक यह है कि विभिन्न आरेख प्रकारों में ब्लॉक्स को एक जैसे मानना बिना उनके विशिष्ट कार्यों के ध्यान में रखे। एक ब्लॉक परिभाषा आरेख (BDD) में, आप प्रणाली के अब्स्ट्रैक्शन को परिभाषित करते हैं। एक आंतरिक ब्लॉक आरेख (IBD) में, आप उस प्रणाली के आंतरिक संरचना और संबंधों को परिभाषित करते हैं।

- गलत तरीका:BDD पर सीधे पोर्ट, धाराएँ और कनेक्टर परिभाषित करना। BDD केवल ब्लॉक्स के बीच क्लास-जैसी परिभाषाओं और संबंधों पर ध्यान केंद्रित करना चाहिए, आंतरिक कनेक्टिविटी पर नहीं।

- प्रभाव:सत्यापन उपकरण इन आरेखों को संरचनात्मक रूप से अस्पष्ट चिह्नित करते हैं। आवश्यकताओं से आंतरिक कार्यान्वयन तक ट्रेसेबिलिटी टूट जाती है।

- सुधार:ब्लॉक हायरार्की और गुणों को परिभाषित करने के लिए BDD का उपयोग करें। IBD का उपयोग केवल भागों, पोर्ट्स और उनके आंतरिक संबंधों को परिभाषित करने के लिए करें। सुनिश्चित करें कि IBD में ब्लॉक BDD में परिभाषित ब्लॉक को संदर्भित करता है।

1.2 पोर्ट मिसमैच और फ्लो समस्याएँ 🔄

पोर्ट डेटा और ऊर्जा आदान-प्रदान के लिए इंटरफेस बिंदु होते हैं। इंटरफेस परिभाषाओं और वास्तविक उपयोग के बीच असंगति सत्यापन विफलता के सामान्य कारण हैं।

- गलत तरीका:इंटरफेस प्रकार की जांच किए बिना एक मानक पोर्ट को एक संदर्भ पोर्ट से जोड़ना। फ्लो की दिशात्मकता (भेजना बनाम प्राप्त करना) को नजरअंदाज करना।

- प्रभाव:मॉडल व्यवहार को सटीक रूप से सिमुलेट नहीं कर सकता है। इंटरफेस जुड़े दिख सकते हैं, लेकिन नीचे के प्रकार मेल नहीं खाते, जिससे अर्थपूर्ण त्रुटियाँ उत्पन्न होती हैं।

- सुधार:सुनिश्चित करें कि प्रत्येक कनेक्टर संगत पोर्ट प्रकारों को जोड़ता है। पोर्ट्स के लिए मानक व्यवहार परिभाषित करने के लिए इंटरफेस ब्लॉक का उपयोग करें। यह सुनिश्चित करें कि फ्लो दिशा इंटरफेस परिभाषा के साथ मेल खाती है (उदाहरण के लिए, सिग्नल फ्लो बनाम भाग फ्लो)।

1.3 अनुपस्थित या अस्पष्ट संदर्भ गुणधर्म 📉

संदर्भ गुणधर्म ब्लॉक्स के बीच संबंधों को परिभाषित करते हैं (उदाहरण के लिए, एक नियंत्रण इकाई एक सेंसर को नियंत्रित करती है)। इन्हें छोड़ देना या गलत तरीके से परिभाषित करना घटकों के बीच तार्किक संबंध को तोड़ देता है।

- गलत तरीका:ब्लॉक परिभाषा में औपचारिक संदर्भ गुणधर्म के बिना, केवल IBD में कनेक्टरों पर भरोसा करके स्वामित्व या नियंत्रण संबंधों का प्रतिनिधित्व करना।

- प्रभाव:प्रणाली संरचना के लिए प्रश्न विफल हो जाते हैं। आप आसानी से बिल ऑफ मेटेरियल (BOM) या प्रोग्रामेटिक रूप से प्रणाली के हायरार्की का निर्धारण नहीं कर सकते हैं।

- सुधार:ब्लॉक परिभाषा के भीतर संदर्भ गुणधर्म परिभाषित करें। इन गुणधर्मों का उपयोग IBD में संबंध को वास्तविक रूप देने के लिए करें। इससे संबंध की परिभाषा और संबंध के विशिष्ट उदाहरण को अलग किया जाता है।

2. व्यवहारात्मक मॉडलिंग की फंदी ⚙️

व्यवहार आरेख यह बताते हैं कि प्रणाली समय के साथ या विशिष्ट स्थितियों के तहत कैसे व्यवहार करती है। यहाँ की त्रुटियाँ ऐसे मॉडल बनाती हैं जिनका सिमुलेशन या संचालन परिदृश्यों के खिलाफ सत्यापन नहीं किया जा सकता।

2.1 स्थिति मशीन संक्रमण ट्रिगर्स 🚦

स्थिति मशीनों का राज्य-निर्भर तर्क को परिभाषित करने के लिए महत्वपूर्ण भूमिका होती है। एक सामान्य त्रुटि घटना ट्रिगर्स और गार्ड शर्तों की परिभाषा से संबंधित होती है।

- गलत तरीका: बूलियन व्यंजकों का उपयोग करना जो कार्यान्वित नहीं हो सकते हैं या राज्य संदर्भ में अस्तित्व में नहीं आने वाले चरों को संदर्भित करना।

- प्रभाव: सिमुलेशन इंजन संक्रमणों का मूल्यांकन नहीं कर सकते हैं। डायनामिक विश्लेषण के दौरान मॉडल लटक जाता है या अप्रत्याशित रूप से व्यवहार करता है।

- सुधार: सुनिश्चित करें कि सभी ट्रिगर घटनाओं को सिग्नल या संक्रमण के रूप में परिभाषित किया गया हो। गार्ड शर्तों में वर्तमान संदर्भ में उपलब्ध मान्य पैरामीटर या गुणों को संदर्भित करना आवश्यक है। सुनिश्चित करें कि प्रत्येक राज्य के लिए निकास मार्ग है, जब तक कि यह अंतिम राज्य न हो।

2.2 गतिविधि आरेख फ्लो नियंत्रण 📊

गतिविधि आरेख नियंत्रण और डेटा के प्रवाह को मॉडल करते हैं। खराब फ्लो नियंत्रण सिमुलेशन में डेडलॉक या अनंत लूप की ओर जाता है।

- गलत तरीका: निकास शर्तों के बिना चक्रीय निर्भरता बनाना। नोड्स पर इनपुट और आउटपुट पिन को सही तरीके से परिभाषित करने में विफलता।

- प्रभाव: सत्यापन उपकरण अपहुंच योग्य नोड्स या चक्करों की रिपोर्ट करते हैं जो समाप्ति को रोकते हैं।

- सुधार: डेटा प्रवाह को स्पष्ट रूप से मैप करें। सुनिश्चित करें कि प्रत्येक निर्णय नोड के लिए एक सत्य/असत्य मार्ग है जो अंततः समाप्त होता है। डेटा संदर्भ को खोए बिना प्रवाहों को मिलाने के लिए मर्ज नोड्स का सही तरीके से उपयोग करें।

2.3 अंतरक्रिया और क्रम में असंगति 📞

क्रम आरेख वस्तुओं के समय के साथ अंतरक्रिया को दिखाते हैं। यहाँ की त्रुटियाँ अक्सर असंगत जीवन रेखाओं या संदेश क्रम के कारण होती हैं।

- गलत तरीका: वर्तमान संदर्भ में अस्तित्व में नहीं आने वाली वस्तुओं को संदेश भेजना या निष्पादन के क्रम को नजरअंदाज करना।

- प्रभाव: इंटरफेस सत्यापन विफल हो जाता है। क्रम में ऑपरेशन का भौतिक वास्तविकता को प्रतिबिंबित नहीं करता है।

- सुधार: जीवन रेखाओं को परिभाषित भागों के साथ संरेखित करें। सुनिश्चित करें कि संदेश क्रम कारणता को प्रतिबिंबित करता है। शर्ती तर्क को सही तरीके से संभालने के लिए संयुक्त अंशों (alt, opt, loop) का उपयोग करें।

3. आवश्यकताएँ और ट्रेसेबिलिटी के अंतराल 📋

MBSE का मुख्य मूल्य ट्रेसेबिलिटी है। यदि आवश्यकताओं को डिज़ाइन तत्वों से जोड़ा नहीं गया है, तो मॉडल का सत्यापन उद्देश्य खो जाता है।

3.1 टूटे हुए आवश्यकता ट्रेसेबिलिटी लिंक 🔗

आवश्यकताओं को विशिष्ट प्रणाली तत्वों में आवंटित किया जाना चाहिए। इस आवंटन में अंतराल सत्यापन को असंभव बना देते हैं।

- गलत तरीका: आवश्यकताओं को केवल अन्य आवश्यकताओं से जोड़ना, या उन्हें किसी माता-पिता या बच्चे के बिना असंगत छोड़ देना।

- प्रभाव: सत्यापन मैट्रिक्स उत्पन्न नहीं किए जा सकते हैं। स्टेकहोल्डर्स को नहीं पता चलता कि आवश्यकता कैसे पूरी की जाती है।

- सुधार: स्पष्ट व्यवस्था स्थापित करें: सिस्टम आवश्यकता -> कार्यात्मक आवश्यकता -> डिज़ाइन तत्व। इन लिंक्स को दृश्यमान बनाने के लिए आवश्यकता आरेख का उपयोग करें। सुनिश्चित करें कि प्रत्येक आवश्यकता कम से कम एक आवंटन मार्ग के साथ हो।

3.2 आवश्यकताओं में मिश्रित विस्तार 🧩

आवश्यकताओं को परमाणु होना चाहिए। एक ही आवश्यकता में उच्च स्तर के लक्ष्यों और निम्न स्तर के कार्यान्वयन विवरणों को मिलाना भ्रम पैदा करता है।

- गलत तरीका: आवश्यकताओं को लिखना जिसमें एक साथ “क्या” और “कैसे” दोनों हों (उदाहरण के लिए, “प्रणाली को प्रकाश चालू करने के लिए 5V पावर सप्लाई का उपयोग करना होगा”)।

- प्रभाव: सत्यापन विफल हो जाता है क्योंकि डिज़ाइन बदल जाता है, लेकिन आवश्यकता वही रहती है। यह असंभव हो जाता है कि आवश्यकता पूरी हुई है या नहीं, यह निर्धारित करना।

- सुधार: “क्या” (कार्यक्षमता) पर आधारित आवश्यकताओं को लिखें। “कैसे” (कार्यान्वयन) को डिज़ाइन सीमाओं या विवरणों में स्थानांतरित करें। इससे डिज़ाइन को आवश्यकताओं को फिर से लिखे बिना विकसित करने की अनुमति मिलती है।

4. सत्यापन और मान्यता (V&V) एकीकरण समस्याएं ✅

मान्यता सुनिश्चित करती है कि सही प्रणाली बनाई गई है; सत्यापन सुनिश्चित करता है कि प्रणाली सही तरीके से बनाई गई है। SysML सत्यापन मानदंडों के माध्यम से इसका समर्थन करता है।

4.1 सत्यापन मानदंडों की अनुपस्थिति 📝

प्रत्येक आवश्यकता जिसके सत्यापन की आवश्यकता हो, के मॉडल में संबंधित सत्यापन विधि परिभाषित होनी चाहिए।

- गलत तरीका:एक आवश्यकता को परिभाषित करना लेकिन सत्यापन फ़ील्ड को खाली या सामान्य छोड़ देना।

- प्रभाव: मॉडल को आवश्यकता के विरुद्ध सत्यापित नहीं किया जा सकता है। परीक्षण मामलों को स्वचालित रूप से उत्पन्न नहीं किया जा सकता है।

- सुधार: प्रत्येक आवश्यकता के लिए विशिष्ट सत्यापन मानदंड परिभाषित करें। इन मानदंडों को परीक्षण मामलों या सिमुलेशन परिदृश्य से जोड़ें। सुनिश्चित करें कि मानदंड मापने योग्य और परीक्षण योग्य हो।

4.2 सीमा संतुष्टि विफलताएं 🧮

OCL (वस्तु सीमा भाषा) या अन्य सीमा तंत्र का उपयोग नियमों को लागू करने के लिए किया जाता है। गलत वाक्य रचना या तर्क सत्यापन को तोड़ देता है।

- गलत तरीका: अस्तित्वहीन गुणों या तर्कपूर्ण ऑपरेटरों को संदर्भित करने वाली सीमाओं का उपयोग करना, जो विरोधाभास पैदा करते हैं।

- प्रभाव: मॉडल संतुष्ट नहीं हो पाता है। परिभाषित सीमाओं के लिए कोई वैध समाधान नहीं है।

- सुधार: प्रतिबंध वाक्य रचना को लागू करने से पहले सत्यापित करें। नमूना डेटा के साथ प्रतिबंधों का परीक्षण करें। सुनिश्चित करें कि प्रतिबंध बाकी मॉडल तर्क के साथ संगत हैं।

5. प्रक्रिया और संस्करण त्रुटियाँ 📂

यहाँ तक कि एक सही मॉडल भी वैलिडेशन में विफल हो सकता है यदि उसके चारों ओर की प्रक्रिया दोषपूर्ण है। संस्करण नियंत्रण और आधार रेखा निर्माण महत्वपूर्ण हैं।

5.1 आधार रेखा निर्माण की कमी 🏁

आधार रेखा के बिना, आप परिवर्तनों को ट्रैक नहीं कर सकते या ज्ञात अच्छी स्थिति में वापस जा सकते हैं।

- गलत तरीका: मॉडल की स्थिति के स्नैपशॉट सेव न करके लगातार परिवर्तन करना।

- प्रभाव: रिग्रेशन समस्याएँ आसानी से अलग नहीं की जा सकती हैं। वैलिडेशन परिणाम स्पष्ट कारण के बिना उतार-चढ़ाव करते हैं।

- सुधार: महत्वपूर्ण चरणों पर आधार रेखा बनाएँ। भंडारण में मॉडल संस्करणों को टैग करें। आधार रेखाओं के बीच क्या परिवर्तन हुआ है, इसका दस्तावेजीकरण करें।

5.2 असंगत नामकरण प्रथाएँ 🏷️

नाम अद्वितीय और वर्णनात्मक होने चाहिए। अस्पष्टता भ्रम और वैलिडेशन त्रुटियों का कारण बनती है।

- गलत तरीका: “Block1”, “PortA”, या “Requirement1” जैसे सामान्य नामों का उपयोग करना।

- प्रभाव: स्वचालित उपकरण रिपोर्ट नहीं बना सकते। मानव बिना संदर्भ के मॉडल को समझ नहीं पाते हैं।

- सुधार: नामकरण मानक अपनाएँ (उदाहरण के लिए, “Sys-Function-001”, “Part-Hydraulic-01”)। मॉडल टेम्पलेट या चेक स्क्रिप्ट के माध्यम से इस मानक को लागू करें।

सामान्य त्रुटियाँ बनाम सुधारात्मक कार्रवाई सारणी 📊

निम्नलिखित सारणी महत्वपूर्ण गलतियों और उनके समाधानों का सारांश प्रदान करती है जिससे त्वरित संदर्भ मिल सके।

| श्रेणी | सामान्य गलती | वैलिडेशन पर प्रभाव | सुधारात्मक कार्रवाई |

|---|---|---|---|

| संरचना | IBD के बजाय BDD पर पोर्ट को परिभाषित करना | अर्थग्राही अस्पष्टता, टूटी हुई कनेक्टिविटी | पोर्ट परिभाषाओं को आंतरिक ब्लॉक आरेख में स्थानांतरित करें |

| व्यवहार | राज्य मशीन में वृत्ताकार संक्रमण | सिमुलेशन में अनंत लूप, अवरोध | निश्चित करें कि निकास मार्ग और वैध गार्ड शर्तें हों |

| आवश्यकताएं | अनाथ आवश्यकताएं | ट्रेसेबिलिटी का अंतराल, सत्यापन योग्य विवरण नहीं | आवश्यकताओं को ब्लॉक्स और गतिविधियों से जोड़ें |

| सत्यापन | सत्यापन मानदंड की कमी | परीक्षण मामलों को उत्पन्न नहीं किया जा सकता | हर आवश्यकता में सत्यापन मानदंड जोड़ें |

| प्रक्रिया | सामान्य नामकरण प्रथाएं | भ्रम, खराब रिपोर्टिंग | कठोर नामकरण मानकों को लागू करें |

गहन अध्ययन: सीमा तर्क और डेटा प्रकार 🧠

एक सूक्ष्म क्षेत्र जहां मॉडल अक्सर विफल होते हैं, वह सीमाओं के भीतर डेटा प्रकारों के प्रबंधन है। SysML मूलभूत प्रकारों का समर्थन करता है, लेकिन जटिल प्रणालियों को अक्सर कस्टम प्रकारों की आवश्यकता होती है।

6.1 इकाई असंगति ⚖️

भौतिकी-आधारित प्रणालियां इकाइयों पर निर्भर करती हैं (उदाहरण के लिए, मीटर, सेकंड, वोल्ट)। बिना रूपांतरण के इकाइयों को मिलाने से सत्यापन विफलता होती है।

- समस्या:इकाइयों को निर्दिष्ट किए बिना एक गुण को “लंबाई” के रूप में परिभाषित करना, फिर इसकी तुलना इकाइयों वाले मान से करना।

- समाधान:जहां टूलिंग समर्थन करती है, वहां इकाई-संवेदनशील गुणों का उपयोग करें। सुनिश्चित करें कि सभी अंकगणितीय संचालन इकाई रूपांतरण नियमों का सम्मान करें।

6.2 पैरामीटर प्रसार 📈

पैरामीटर गुणों के मानों को परिभाषित करते हैं। यदि पैरामीटरों को विवरणात्मक संरचना के माध्यम से सही ढंग से प्रसारित नहीं किया जाता है, तो मान खो जाते हैं।

- समस्या:शीर्ष स्तर पर एक पैरामीटर को परिभाषित करना, लेकिन उन बच्चे ब्लॉक्स को आवंटित न करना जिन्हें इसकी आवश्यकता है।

- समाधान:पैरामीटरों को विवरणात्मक संरचना के माध्यम से नीचे ले जाने के लिए आवंटन संबंध का उपयोग करें। सुनिश्चित करें कि बच्चे ब्लॉक्स पैरामीटर सीमाओं को विरासत में प्राप्त करते हैं।

लंबे समय तक मॉडल स्वास्थ्य सुनिश्चित करना 🛡️

सत्यापन त्रुटियों को ठीक करना एक बार का कार्य नहीं है। स्वस्थ मॉडल को बनाए रखने के लिए अनुशासन की आवश्यकता होती है।

- नियमित ऑडिट: मॉडल संरचना और व्यवहार की नियमित समीक्षा की योजना बनाएं। अनप्रयुक्त ब्लॉक या असंबंधित आवश्यकताओं की जांच करें।

- स्वचालित जांचें: यदि आपका मॉडलिंग वातावरण इसकी अनुमति देता है, तो सहेजने पर स्वचालित रूप से सत्यापन जांच करने के लिए स्क्रिप्ट का उपयोग करें।

- प्रशिक्षण: सुनिश्चित करें कि सभी मॉडलर BDD और IBD के बीच अंतर और आवश्यकता आवंटन के नियमों को समझते हैं।

- दस्तावेज़ीकरण: मॉडलिंग मानक दस्तावेज़ को बनाए रखें। नए टीम सदस्यों के एकीकरण के समय इसका संदर्भ लें।

इन विशिष्ट क्षेत्रों को संबोधित करके, आप एक नाजुक मॉडल से बाहर निकलते हैं जो समीक्षा के तहत टूट जाता है, और एक दृढ़ संपत्ति में बदल जाता है जो इंजीनियरिंग आत्मविश्वास को बढ़ाता है। सत्यापन एक गेट पार करने के लिए नहीं है; यह एक निरंतर प्रतिक्रिया लूप है जो सुनिश्चित करता है कि मॉडल प्रणाली का सटीक प्रतिनिधित्व बना रहे।

संरचना पर ध्यान केंद्रित करें, व्यवहार को लागू करें, आवश्यकताओं को जोड़ें, और सीमाओं की पुष्टि करें। इस अनुशासित दृष्टिकोण से तकनीकी दायित्व कम होता है और यह सुनिश्चित करता है कि आपका MBSE कार्यान्वयन अवधारणा से लेकर निष्क्रियता तक मूल्य प्रदान करता है।