Pengantar Tantangan Integrasi 💡

Rekayasa sistem secara inheren kompleks. Ketika berpindah dari model konseptual ke perangkat keras fisik, ruang untuk kesalahan berkurang secara signifikan. Salah satu bidang paling kritis di mana proyek sering mengalami kegagalan adalah jejak kebutuhan. Studi kasus ini meninjau skenario dunia nyata di mana upaya integrasi perangkat keras gagal, bukan karena kurangnya keterampilan teknis, tetapi karena kegagalan dalam menghubungkan kebutuhan dengan perilaku sistem dalam kerangka kerja Bahasa Pemodelan Sistem (SysML). Tujuannya adalah mengurai titik-titik kegagalan, memahami implikasi teknisnya, dan menguraikan bagaimana pemodelan yang ketat dapat mencegah hasil serupa.

Jejak kebutuhan lebih dari sekadar item daftar periksa. Ini adalah tulang punggung integritas sistem. Ketika suatu kebutuhan tidak dikaitkan dengan elemen desain, tidak ada cara untuk memverifikasi apakah elemen tersebut benar-benar memenuhi tujuannya. Dalam lingkungan berisiko tinggi, seperti pengembangan penerbangan atau kendaraan otonom, ketidaksesuaian ini dapat menyebabkan pekerjaan ulang yang mahal, penundaan jadwal, dan risiko keselamatan. Analisis ini berfokus pada mekanisme kegagalan dan konstruksi SysML khusus yang kurang dimanfaatkan atau digunakan secara keliru.

Latar Belakang dan Lingkup Proyek 📦

Proyek yang dimaksud melibatkan pengembangan unit fusi multi-sensor untuk platform navigasi otonom. Sistem ini membutuhkan integrasi LIDAR, radar, dan kamera optik ke dalam satu node pemrosesan yang terpadu. Siklus pengembangan mengikuti pendekatan Rekayasa Sistem Berbasis Model (MBSE), menggunakan SysML untuk menentukan arsitektur dan kebutuhan.

Parameter Proyek Utama:

- Jenis Sistem:Kumpulan Sensor Navigasi Otonom

- Fase Pengembangan:Integrasi Sistem dan Verifikasi

- Teknologi Utama:SysML untuk pemodelan dan spesifikasi

- Hasil:Kegagalan integrasi karena celah kebutuhan yang belum diverifikasi

Tim membuat serangkaian kebutuhan yang komprehensif pada tahap awal. Namun, keterkaitan antara kebutuhan teks tersebut dan blok desain fisik bersifat tidak konsisten. Meskipun arsitektur sistem awal telah dimodelkan, fase integrasi yang mendalam kekurangan ketelitian yang diperlukan dalam rantai jejak kebutuhan. Ketidaksesuaian ini baru terungkap ketika prototipe fisik pertama dirakit.

Peran SysML dalam Rekayasa Sistem Modern 🧩

SysML menyediakan cara standar untuk menggambarkan struktur sistem, perilaku, dan kebutuhan. Dalam model yang terstruktur dengan baik, setiap kebutuhan harus diuraikan, dialokasikan, dan diverifikasi. Bahasa ini mendukung beberapa jenis diagram, termasuk:

- Diagram Kebutuhan:Menentukan ‘apa’ dari sistem.

- Diagram Definisi Blok (BDD):Menentukan ‘struktur’ dari sistem.

- Diagram Blok Internal (IBD):Menentukan ‘antarmuka’ dan koneksi antar blok.

- Diagram Parametrik:Menentukan ‘kendala’ dan hubungan matematis.

Dalam skenario yang dianalisis, Diagram Kebutuhan diisi secara luas. Tim berhasil menangkap kebutuhan fungsional dan non-fungsional. Namun, alokasi kebutuhan-kebutuhan ini ke blok tertentu dalam BDD dan IBD bersifat longgar. Banyak kebutuhan dibiarkan terpisah, artinya ada dalam model tetapi tidak memiliki hubungan keluar ke elemen desain. Hal ini menciptakan rasa lengkap yang menyesatkan. Model terlihat terisi, tetapi alur logis verifikasi telah terputus.

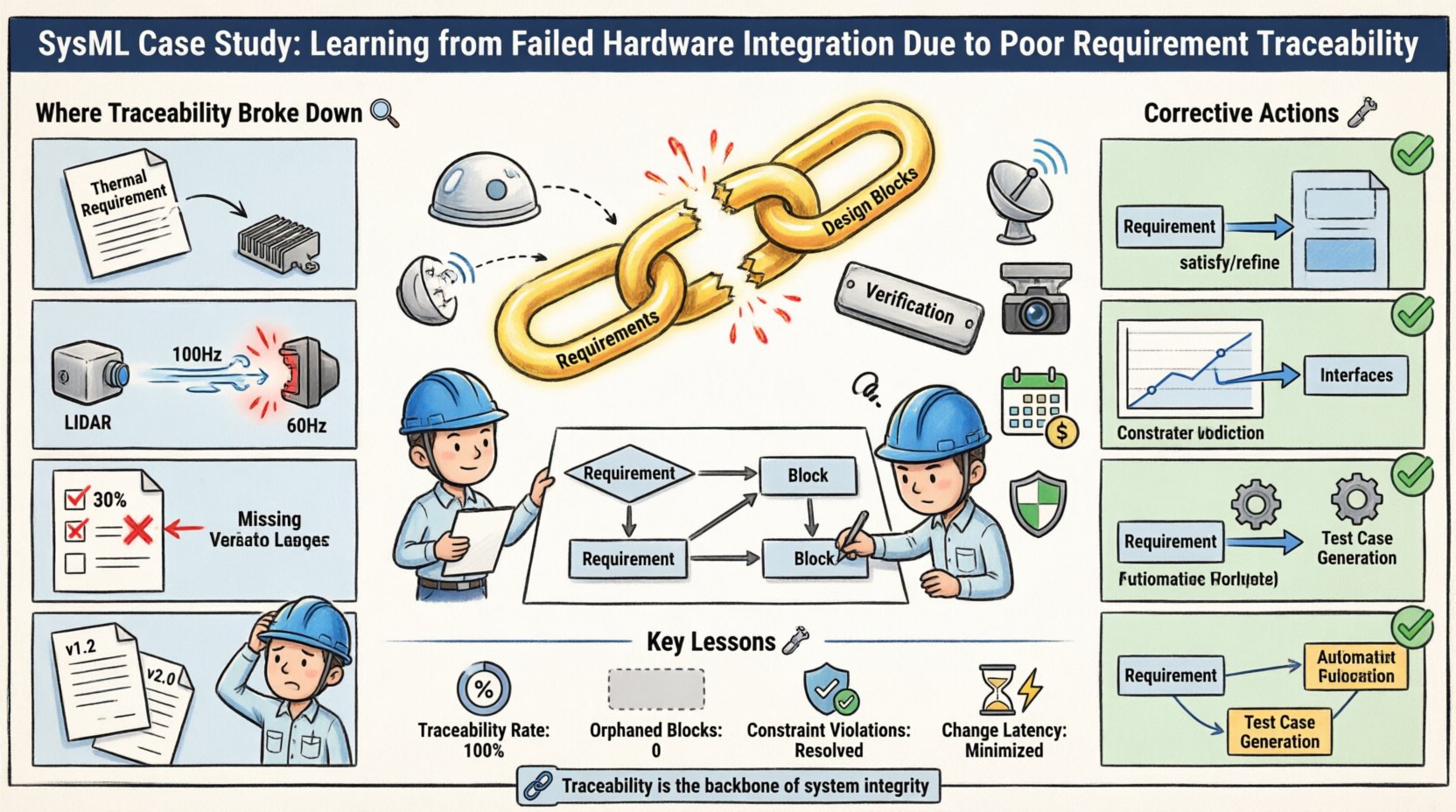

Di Mana Jejak Kebutuhan Gagal 🔍

Kegagalan bukanlah kejadian tunggal, tetapi serangkaian kelalaian kecil yang berkembang seiring waktu. Poin-poin berikut menjelaskan di mana rantai jejak kebutuhan retak selama proses pemodelan.

1. Alokasi Kebutuhan yang Tidak Konsisten

Selama tahap analisis kebutuhan, insinyur mengalokasikan kebutuhan ke blok-blok sistem tingkat tinggi. Saat desain berpindah ke subsistem, alokasi ini tidak disebarkan ke bawah. Sebagai contoh, kebutuhan manajemen termal dialokasikan ke blok “Unit Sensor” tetapi tidak pernah terhubung ke komponen spesifik “Heat Sink” dalam diagram blok internal. Ketika perangkat keras diproduksi, heat sink terlalu kecil karena kebutuhan termal tidak secara aktif mendorong batasan desain.

2. Kesenjangan Definisi Antarmuka

Diagram Blok Internal mendefinisikan port dan konektor antar komponen. Dalam kasus ini, antarmuka aliran data dimodelkan, tetapi persyaratan waktu sinyal tidak terhubung ke port antarmuka. Aliran data LIDAR diharapkan berjalan pada 100Hz, tetapi kebutuhan yang menentukan frekuensi ini tidak terlampir ke port antarmuka komunikasi. Akibatnya, pengendali antarmuka dirancang untuk 60Hz, menyebabkan kehilangan data saat integrasi.

3. Tautan Verifikasi Hilang

Model yang kuat membutuhkan tautan verifikasi. Ini menghubungkan kebutuhan ke kasus uji atau elemen desain tertentu yang membuktikan kebutuhan terpenuhi. Tim proyek mengabaikan pembuatan tautan verifikasi ini untuk sekitar 30% kebutuhan. Tanpa tautan ini, tidak ada cara otomatis untuk membuat rencana verifikasi. Tahap pengujian menjadi manual dan tidak terencana, menyebabkan area cakupan yang terlewat.

4. Pengendalian Versi dan Perpindahan Basis

Kebutuhan berkembang sepanjang proyek. Permintaan perubahan dibuat untuk menyesuaikan dengan teknologi sensor baru. Namun, model tidak menerapkan pengendalian versi yang ketat pada hubungan antara kebutuhan dan blok. Ketika kebutuhan berubah, blok desain hulu tidak ditandai untuk ditinjau. Perpindahan ini berarti perangkat keras dibangun berdasarkan versi lama spesifikasi, yang tidak lagi terkini dalam model sistem.

Perbandingan Status Pemodelan 📊

Untuk memvisualisasikan kesenjangan antara keadaan yang diinginkan dan keadaan aktual model, pertimbangkan tabel perbandingan berikut. Ini menyoroti area-area tertentu di mana pelacakan tidak memadai.

| Aspek Pelacakan | Keadaan yang Diharapkan (Ideal) | Keadaan Aktual (Diamati) | Masalah yang Timbul |

|---|---|---|---|

| Alokasi Kebutuhan | 100% kebutuhan terhubung ke blok desain | 70% kebutuhan terhubung ke blok desain | Keputusan desain yang tidak diverifikasi |

| Kendala Antarmuka | Waktu sinyal terhubung ke properti port | Kendala waktu hanya dalam bentuk teks | Ketidaksesuaian antarmuka (60Hz vs 100Hz) |

| Tautan Verifikasi | Tautan langsung ke kasus uji | Matriks pelacakan manual | Cakupan uji yang terlewat |

| Manajemen Perubahan | Analisis dampak otomatis saat perubahan | Diperlukan tinjauan manual | Pembuatan perangkat keras yang usang |

Analisis Dampak Mendalam 📉

Konsekuensi dari pelacakan yang buruk terasa langsung dan dapat diukur. Fase integrasi yang direncanakan memakan waktu empat minggu, memanjang menjadi dua belas minggu. Analisis akar masalah mengungkapkan bahwa perangkat keras harus diredesain untuk memenuhi persyaratan awal yang dilupakan selama fase pemodelan.

Implikasi Biaya

Mendesain ulang wadah sensor dan papan antarmuka komunikasi menimbulkan biaya material dan tenaga kerja yang signifikan. Pengadaan komponen baru menyebabkan kenaikan harga karena pengiriman darurat. Melebihi anggaran secara langsung disebabkan oleh pekerjaan ulang yang diperlukan untuk memperbaiki persyaratan yang tidak terhubung.

Keterlambatan Jadwal

Pengujian integrasi tidak dapat dilanjutkan hingga perangkat keras sesuai spesifikasi. Keterlambatan ini menunda fase integrasi perangkat lunak. Karena perangkat lunak bergantung pada sinyal perangkat keras, seluruh jadwal validasi sistem menjadi lebih padat. Ini memaksa tim bekerja lembur untuk memenuhi tenggat peluncuran, meningkatkan risiko munculnya kesalahan baru.

Risiko Keselamatan

Dampak paling kritis melibatkan keselamatan. Kegagalan manajemen termal berarti sensor bisa terlalu panas dalam kondisi suhu lingkungan tinggi. Hal ini tidak terdeteksi selama pengujian awal karena persyaratan termal tidak dipantau secara aktif dalam model. Dalam lingkungan produksi, hal ini bisa menyebabkan kegagalan sistem saat beroperasi, membahayakan personel dan properti.

Tindakan Korektif dan Peningkatan SysML 🛠️

Setelah kegagalan teridentifikasi, tim teknik menerapkan strategi korektif yang berfokus pada penguatan rantai pelacakan dalam model SysML. Langkah-langkah berikut diambil untuk memulihkan integritas definisi sistem.

1. Aturan Alokasi yang Ditegakkan

Tim menetapkan aturan bahwa tidak ada persyaratan yang boleh dipindahkan ke tahap pengembangan berikutnya tanpa alokasi yang sah ke blok desain. Aturan ini ditegakkan melalui skrip validasi model. Jika suatu persyaratan tidak memiliki hubungan keluaran ‘memenuhi’ atau ‘memperbaiki’, model akan menandainya sebagai tidak lengkap. Ini memaksa insinyur untuk menghubungkan setiap persyaratan dengan komponen fisik atau logis.

2. Integrasi Kendala Antarmuka

Persyaratan waktu sinyal dan laju data dipindahkan dari dokumen teks ke dalam diagram parametrik. Diagram ini kini secara eksplisit membatasi sifat port antarmuka. Ini memastikan bahwa jika suatu persyaratan berubah, kendala antarmuka akan diperbarui secara otomatis, memicu pemberitahuan ke tim desain.

3. Perencanaan Verifikasi Otomatis

Tim menerapkan alur kerja di mana tautan verifikasi menghasilkan kasus uji secara otomatis. Setiap persyaratan dengan tautan verifikasi menciptakan item uji yang tertunda dalam sistem manajemen kualitas. Ini memastikan bahwa tidak ada persyaratan yang diverifikasi tanpa rencana uji yang sesuai. Ini mengurangi risiko kesalahan manual dalam melacak cakupan uji.

4. Analisis Dampak Perubahan

Ketika suatu persyaratan diubah, model diquery untuk menemukan semua ketergantungan hulu. Setiap blok yang memenuhi atau memperbaiki persyaratan tersebut ditandai. Umpan balik visual ini memungkinkan tim melihat secara tepat komponen perangkat keras mana yang perlu dievaluasi ulang sebelum menerapkan perubahan.

Pelajaran untuk Proyek Masa Depan 🚀

Studi kasus ini memberikan beberapa pelajaran bagi tim rekayasa sistem yang menerapkan MBSE. Pelajaran utama adalah bahwa model hanya sebaik hubungan yang ada di dalamnya. Model yang penuh dengan elemen yang terputus tidak memberikan nilai apa pun selama integrasi.

- Pelacakan adalah Proses Berkelanjutan: Ini bukan tugas yang harus diselesaikan di akhir tahap. Pelacakan harus dipertahankan sepanjang siklus hidup seiring berkembangnya persyaratan.

- Tautan Menggerakkan Desain: Persyaratan harus menggerakkan penciptaan elemen desain, bukan sebaliknya. Jika suatu elemen desain ada tanpa persyaratan, secara teknis itu merupakan utang teknis.

- Validasi adalah Kunci: Tautan verifikasi harus dibuat sejak awal. Menunggu hingga perangkat keras selesai dibuat untuk memverifikasi persyaratan terlalu terlambat.

- Dukungan Alat Bantu: Meskipun alat perangkat lunak tidak disebutkan secara khusus, kemampuan untuk menanyakan hubungan dan memvisualisasikan ketergantungan sangat penting. Pelacakan manual rentan terhadap kesalahan.

Menerapkan Rantai Pelacakan yang Kuat 🔗

Untuk mencegah terulangnya, daftar periksa berikut harus diterapkan pada semua model SysML sebelum beralih ke fabrikasi perangkat keras.

Daftar Periksa Pra-Integrasi

- Cakupan Persyaratan:Apakah semua persyaratan dialokasikan ke setidaknya satu blok?

- Kelengkapan Antarmuka:Apakah semua antarmuka fisik memiliki tipe data dan batasan waktu yang didefinisikan?

- Validasi Kendala:Apakah kendala parametrik dipenuhi oleh nilai desain saat ini?

- Tautan Verifikasi:Apakah setiap persyaratan memiliki jalur ke kasus uji atau metode validasi?

- Riwayat Perubahan:Apakah versi model disinkronkan dengan versi spesifikasi perangkat keras?

Metrik Pemantauan

Tim harus melacak metrik tertentu untuk memastikan kesehatan pelacakan. Metrik-metrik ini dapat diekstrak dari repositori model.

- Tingkat Pelacakan:Persentase persyaratan dengan tautan yang valid.

- Blok Terlantar:Jumlah blok desain yang tidak memiliki persyaratan terkait.

- Pelanggaran Kendala:Jumlah kendala parametrik yang saat ini dilanggar.

- Latensi Perubahan:Waktu yang berlalu antara perubahan persyaratan dan pembaruan model.

Pikiran Akhir tentang Teknik Rekayasa Sistem Berbasis Model 🏁

Kegagalan yang dijelaskan dalam studi kasus ini berfungsi sebagai pengingat yang tegas akan pentingnya disiplin dalam rekayasa sistem. SysML adalah alat yang kuat yang memungkinkan kejelasan dan ketelitian, tetapi memerlukan manajemen aktif. Teknologi ini tidak secara otomatis menerapkan praktik baik; insinyur harus menentukan dan menerapkannya.

Dengan memperlakukan model sebagai satu-satunya sumber kebenaran dan memastikan setiap baris kode dan setiap komponen pada papan sirkuit dapat dilacak kembali ke persyaratan tertentu, organisasi dapat mengurangi risiko kegagalan integrasi. Jalur menuju integrasi perangkat keras yang sukses dipenuhi oleh rantai pelacakan yang jelas dan utuh. Ketika rantai ini terputus, sistem fisik mengalami kerugian. Ketika rantai tersebut kuat, sistem menjadi tangguh, handal, dan selaras dengan tujuan awalnya.

Proyek-proyek masa depan harus berinvestasi dalam pelatihan dan definisi proses mengenai pelacakan. Ini mencakup menentukan apa yang membentuk tautan yang valid dan menetapkan tata kelola terhadap perubahan model. Biaya pencegahan selalu lebih rendah daripada biaya koreksi. Dalam konteks integrasi perangkat keras yang kompleks, perbedaan antara keberhasilan dan kegagalan sering terletak pada detail bagaimana persyaratan terhubung dalam model.