Engineering Sistem Berbasis Model (MBSE) telah mengubah cara sistem kompleks dirancang, dianalisis, dan divalidasi. Dengan beralih dari proses berbasis dokumen ke alur kerja berbasis model, organisasi mendapatkan satu sumber kebenaran tunggal untuk arsitektur sistem. Namun, transisi ke Bahasa Pemodelan Sistem (SysML) menimbulkan tantangan teknis tertentu. Banyak tim rekayasa mengalami kegagalan validasi yang menghambat kemajuan, mengaburkan pelacakan, dan merusak integritas sistem.

Ketika model SysML gagal divalidasi, bukan hanya kesalahan sintaks; seringkali merupakan gejala dari pemahaman konseptual yang keliru mengenai definisi blok, aliran perilaku, atau alokasi kebutuhan. Kesalahan-kesalahan ini menyebar sepanjang siklus rekayasa, menyebabkan pekerjaan ulang yang mahal selama tahap integrasi atau pengujian. Panduan ini menjelaskan kesalahan paling umum yang ditemui dalam pemodelan SysML dan memberikan tindakan korektif nyata untuk memulihkan kesehatan model serta memastikan kepatuhan validasi.

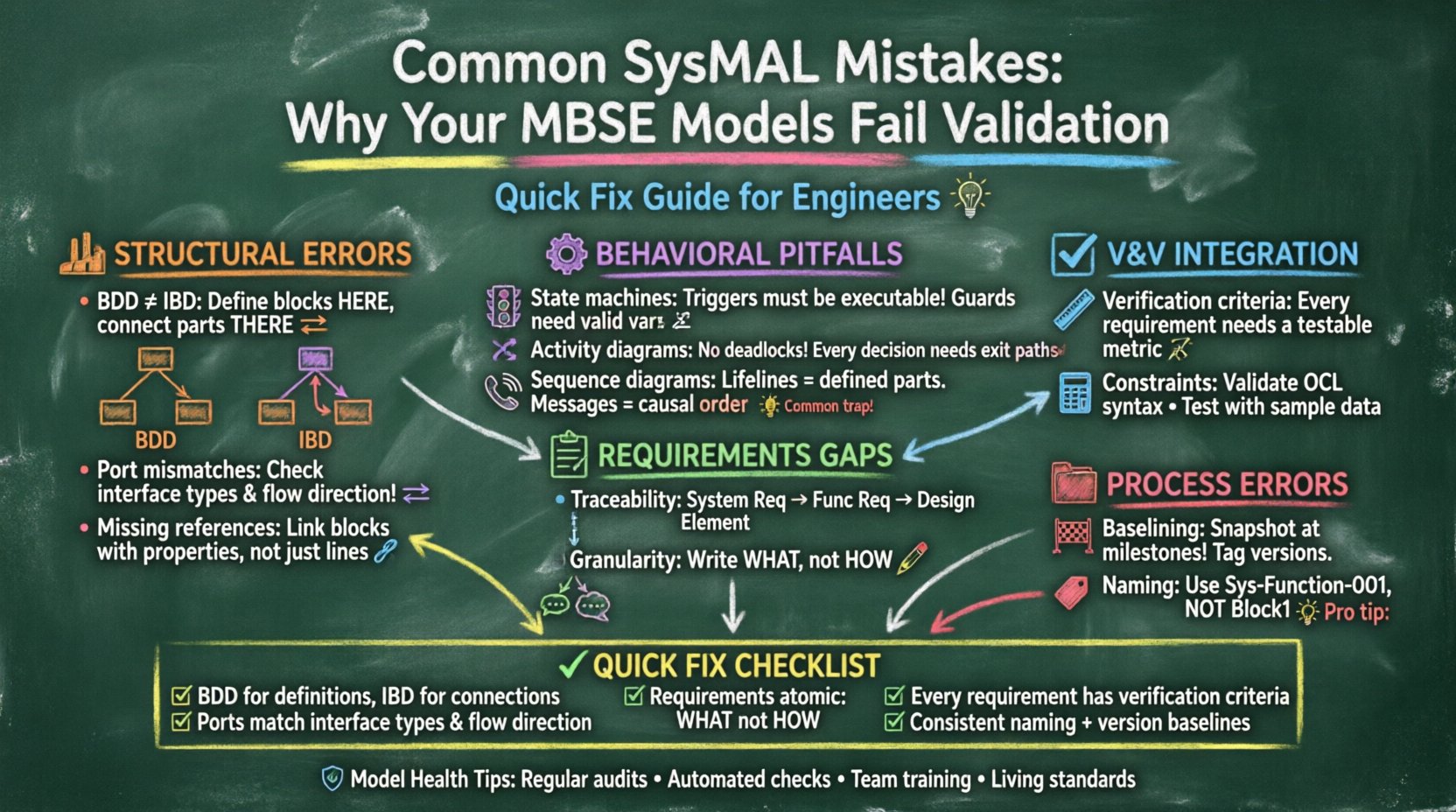

1. Kesalahan Pemodelan Struktural 🏗️

Dasar dari setiap model SysML terletak pada definisi strukturalnya. Kesalahan di sini menyebar ke luar, memengaruhi perilaku dan kebutuhan. Struktur yang kuat memastikan bahwa bagian, port, dan koneksi didefinisikan secara logis.

1.1 Mengaburkan Diagram Definisi Blok (BDD) dan Diagram Blok Internal (IBD) 📐

Salah satu kesalahan yang paling umum adalah memperlakukan Blok sebagai sesuatu yang dapat dipertukarkan di berbagai jenis diagram tanpa memperhatikan peran khususnya. Pada Diagram Definisi Blok (BDD), Anda mendefinisikan abstraksi dari suatu sistem. Pada Diagram Blok Internal (IBD), Anda mendefinisikan komposisi internal dan koneksi dari sistem tersebut.

- Pendekatan yang Salah: Mendefinisikan port, aliran, dan konektor langsung pada BDD. BDD harus fokus pada definisi mirip kelas dan hubungan antar blok, bukan konektivitas internal.

- Dampak:Alat validasi menandai diagram ini sebagai ambigu secara struktural. Pelacakan dari kebutuhan ke implementasi internal menjadi terputus.

- Koreksi: Gunakan BDD untuk mendefinisikan hierarki dan properti blok. Gunakan IBD secara eksklusif untuk mendefinisikan bagian, port, dan koneksi internalnya. Pastikan Blok di IBD merujuk pada Blok yang didefinisikan di BDD.

1.2 Ketidaksesuaian Port dan Masalah Aliran 🔄

Port adalah titik antarmuka untuk pertukaran data dan energi. Ketidaksesuaian antara definisi antarmuka dan penggunaan aktual merupakan sumber umum kegagalan validasi.

- Pendekatan yang Salah: Menghubungkan port standar ke port referensi tanpa memverifikasi jenis antarmuka. Mengabaikan arah aliran (kirim vs. terima).

- Dampak:Model tidak dapat mensimulasikan perilaku secara akurat. Antarmuka mungkin tampak terhubung, tetapi jenis dasar tidak sesuai, menyebabkan kesalahan semantik.

- Koreksi: Pastikan setiap konektor menghubungkan jenis port yang kompatibel. Gunakan Blok Antarmuka untuk mendefinisikan perilaku standar pada port. Verifikasi bahwa arah aliran sesuai dengan definisi antarmuka (misalnya, aliran sinyal vs. aliran bagian).

1.3 Properti Referensi yang Hilang atau Ambigu 📉

Properti referensi mendefinisikan hubungan antar blok (misalnya, Unit Kontrol mengendalikan Sensor). Mengabaikan atau mendefinisikannya secara salah memutus hubungan logis antar komponen.

- Pendekatan yang Salah: Mengandalkan hanya konektor di IBD untuk mewakili hubungan kepemilikan atau kendali tanpa properti referensi formal dalam definisi Blok.

- Dampak:Pertanyaan tentang komposisi sistem gagal. Anda tidak dapat dengan mudah membuat Daftar Bahan (BOM) atau menentukan hierarki sistem secara otomatis.

- Koreksi: Definisikan properti referensi dalam Definisi Blok. Gunakan properti ini di IBD untuk menginstansiasi hubungan. Ini memisahkan definisi hubungan dari contoh khusus koneksi.

2. Jebakan Pemodelan Perilaku ⚙️

Diagram perilaku menggambarkan bagaimana sistem berperilaku seiring waktu atau dalam kondisi tertentu. Kesalahan di sini menghasilkan model yang tidak dapat disimulasikan atau diverifikasi terhadap skenario operasional.

2.1 Pemicu Transisi Mesin Status 🚦

Mesin status sangat penting untuk mendefinisikan logika yang bergantung pada status. Kesalahan umum melibatkan definisi pemicu peristiwa dan kondisi penjaga.

- Pendekatan yang Salah:Menggunakan ekspresi Boolean yang tidak dapat dieksekusi atau merujuk pada variabel yang tidak ada dalam konteks status.

- Dampak:Mesin simulasi tidak dapat mengevaluasi transisi. Model terjebak atau berperilaku tidak terduga selama analisis dinamis.

- Koreksi:Pastikan semua peristiwa pemicu didefinisikan sebagai sinyal atau transisi. Kondisi penjaga harus merujuk pada parameter atau properti yang valid yang tersedia dalam konteks saat ini. Validasi bahwa setiap status memiliki jalur keluar kecuali jika itu adalah status akhir.

2.2 Pengendalian Alur Diagram Aktivitas 📊

Diagram aktivitas memodelkan alur kontrol dan data. Pengendalian alur yang buruk menyebabkan deadlock atau loop tak terbatas dalam simulasi.

- Pendekatan yang Salah:Menciptakan ketergantungan melingkar tanpa kondisi keluar. Gagal mendefinisikan pin input dan output dengan benar pada node.

- Dampak:Alat validasi melaporkan node yang tidak dapat dijangkau atau siklus yang mencegah terminasi.

- Koreksi:Peta alur data secara eksplisit. Pastikan setiap node keputusan memiliki jalur benar/salah yang pada akhirnya bersatu. Gunakan node penggabung secara benar untuk menggabungkan alur tanpa kehilangan konteks data.

2.3 Ketidaksesuaian Interaksi dan Urutan 📞

Diagram urutan menunjukkan interaksi objek seiring waktu. Kesalahan di sini sering berasal dari garis hidup yang tidak sesuai atau urutan pesan.

- Pendekatan yang Salah:Mengirim pesan ke objek yang tidak ada dalam lingkup saat ini atau mengabaikan urutan eksekusi.

- Dampak:Validasi antarmuka gagal. Urutan operasi tidak mencerminkan realitas fisik sistem.

- Koreksi:Selaraskan garis hidup dengan Bagian yang telah didefinisikan. Pastikan urutan pesan mencerminkan kausalitas. Gunakan fragmen gabungan (alt, opt, loop) untuk menangani logika bersyarat dengan benar.

3. Keterbatasan Kebutuhan dan Pelacakan 📋

Nilai inti dari MBSE adalah pelacakan. Jika kebutuhan tidak dikaitkan dengan elemen desain, model kehilangan tujuan verifikasinya.

3.1 Tautan Pelacakan Kebutuhan yang Putus 🔗

Kebutuhan harus dialokasikan ke elemen sistem tertentu. Kesenjangan dalam alokasi ini membuat verifikasi menjadi tidak mungkin.

- Pendekatan yang Salah: Menghubungkan persyaratan hanya ke persyaratan lainnya, atau meninggalkannya terpisah tanpa tautan induk atau anak.

- Dampak:Matriks verifikasi tidak dapat dibuat. Pihak terkait tidak dapat melihat bagaimana suatu persyaratan dipenuhi.

- Koreksi:Tetapkan hierarki yang jelas: Persyaratan Sistem -> Persyaratan Fungsional -> Elemen Desain. Gunakan diagram Persyaratan untuk memvisualisasikan tautan-tautan ini. Pastikan setiap persyaratan memiliki setidaknya satu jalur alokasi.

3.2 Granularitas Campuran dalam Persyaratan 🧩

Persyaratan harus bersifat atomik. Menggabungkan tujuan tingkat tinggi dengan detail implementasi tingkat rendah dalam satu persyaratan menciptakan kebingungan.

- Pendekatan yang Salah:Menulis persyaratan yang berisi baik ‘apa’ maupun ‘bagaimana’ (misalnya, ‘Sistem harus menggunakan catu daya 5V untuk menyalakan lampu’).

- Dampak:Validasi gagal karena desain berubah, tetapi persyaratan tetap. Menjadi mustahil untuk menentukan apakah persyaratan telah dipenuhi.

- Koreksi:Tulis persyaratan berdasarkan ‘apa’ (fungsionalitas). Pindahkan ‘bagaimana’ (implementasi) ke dalam batasan atau spesifikasi desain. Ini memungkinkan desain berkembang tanpa harus menulis ulang persyaratan.

4. Masalah Integrasi Verifikasi dan Validasi (V&V) ✅

Validasi memastikan sistem yang benar dibangun; verifikasi memastikan sistem dibangun dengan benar. SysML mendukung hal ini melalui kriteria verifikasi.

4.1 Kriteria Verifikasi yang Hilang 📝

Setiap persyaratan yang memerlukan verifikasi harus memiliki metode verifikasi yang sesuai didefinisikan dalam model.

- Pendekatan yang Salah:Mendefinisikan persyaratan tetapi meninggalkan kolom verifikasi kosong atau bersifat umum.

- Dampak:Model tidak dapat divalidasi terhadap persyaratan. Kasus uji tidak dapat dihasilkan secara otomatis.

- Koreksi:Tentukan kriteria verifikasi yang spesifik untuk setiap persyaratan. Hubungkan kriteria ini dengan kasus uji atau skenario simulasi. Pastikan kriteria tersebut dapat diukur dan dapat diuji.

4.2 Kegagalan Memenuhi Kendala 🧮

OCL (Bahasa Kendala Objek) atau mekanisme kendala lainnya digunakan untuk menegakkan aturan. Sintaks atau logika yang salah mengganggu validasi.

- Pendekatan yang Salah:Menggunakan kendala yang merujuk pada properti yang tidak ada atau operator logika yang menciptakan kontradiksi.

- Dampak:Model menjadi tidak dapat dipenuhi. Tidak ada solusi valid yang ada untuk kendala yang didefinisikan.

- Koreksi: Validasi sintaks kendala sebelum menerapkan. Uji kendala dengan data contoh. Pastikan kendala konsisten dengan logika model lainnya.

5. Kesalahan Proses dan Pengelolaan Versi 📂

Bahkan model yang sempurna bisa gagal divalidasi jika proses di sekitarnya bermasalah. Pengendalian versi dan penentuan dasar (baselining) sangat penting.

5.1 Kurangnya Penentuan Dasar (Baselining) 🏁

Tanpa penentuan dasar, Anda tidak dapat melacak perubahan atau kembali ke status yang diketahui baik.

- Pendekatan yang Salah: Melakukan perubahan terus-menerus tanpa menyimpan gambaran (snapshot) dari status model.

- Dampak:Masalah regresi sulit diidentifikasi. Hasil validasi berfluktuasi tanpa alasan yang jelas.

- Perbaikan: Tetapkan dasar pada tahapan kunci. Beri tag versi model di repositori. Dokumentasikan perubahan yang terjadi antar dasar.

5.2 Konvensi Penamaan yang Tidak Konsisten 🏷️

Nama harus unik dan deskriptif. Ambiguitas menyebabkan kebingungan dan kesalahan validasi.

- Pendekatan yang Salah: Menggunakan nama umum seperti “Block1”, “PortA”, atau “Requirement1”.

- Dampak:Alat otomatis tidak dapat menghasilkan laporan. Manusia tidak dapat memahami model tanpa konteks.

- Perbaikan: Terapkan standar penamaan (misalnya, “Sys-Fungsi-001”, “Bagian-Hidrolik-01”). Terapkan standar ini melalui templat model atau skrip pemeriksaan.

Tabel Kesalahan Umum vs. Tindakan Perbaikan 📊

Tabel berikut merangkum kesalahan kritis dan solusinya untuk referensi cepat.

| Kategori | Kesalahan Umum | Dampak terhadap Validasi | Tindakan Perbaikan |

|---|---|---|---|

| Struktur | Mendefinisikan port pada BDD alih-alih IBD | Ambiguitas semantik, koneksi terputus | Pindahkan definisi port ke Diagram Blok Internal |

| Perilaku | Transisi melingkar dalam Mesin Status | Putaran tak terbatas dalam simulasi, deadlock | Pastikan jalur keluar dan kondisi penjaga yang valid |

| Persyaratan | Persyaratan yang terpisah | Kesenjangan pelacakan, spesifikasi yang tidak dapat diverifikasi | Hubungkan persyaratan dengan Blok dan Kegiatan |

| Verifikasi | Kriteria verifikasi yang hilang | Tidak dapat menghasilkan kasus uji | Tambahkan kriteria verifikasi ke setiap persyaratan |

| Proses | Konvensi penamaan umum | Kerancuan, pelaporan yang buruk | Terapkan standar penamaan yang ketat |

Penyelidikan Mendalam: Logika Kendala dan Tipe Data 🧠

Salah satu area yang halus di mana model sering gagal adalah penanganan tipe data dalam kendala. SysML mendukung tipe dasar, tetapi sistem yang kompleks sering membutuhkan tipe khusus.

6.1 Ketidakseragaman Satuan ⚖️

Sistem berbasis fisika bergantung pada satuan (misalnya, meter, detik, volt). Menggabungkan satuan tanpa konversi menyebabkan kegagalan validasi.

- Masalah:Menentukan suatu properti sebagai ‘Panjang’ tanpa menentukan satuan, lalu membandingkannya dengan nilai yang memiliki satuan.

- Solusi:Gunakan properti yang peka satuan jika alat pendukung mendukungnya. Pastikan semua operasi aritmetika mematuhi aturan konversi satuan.

6.2 Penyebaran Parameter 📈

Parameter menentukan nilai-nilai properti. Jika parameter tidak disebarkan dengan benar melalui hierarki, nilai-nilai akan hilang.

- Masalah:Menentukan parameter pada tingkat atas tetapi gagal mengalokasikannya ke blok anak yang membutuhkannya.

- Solusi:Gunakan hubungan alokasi untuk meneruskan parameter ke bawah hierarki. Verifikasi bahwa blok anak mewarisi kendala parameter.

Menjamin Kesehatan Model Jangka Panjang 🛡️

Mengoreksi kesalahan validasi bukanlah tugas satu kali saja. Menjaga model yang sehat membutuhkan disiplin.

- Audit Berkala: Jadwalkan tinjauan berkala terhadap struktur dan perilaku model. Periksa adanya blok yang tidak digunakan atau persyaratan yang terpisah.

- Pemeriksaan Otomatis: Jika lingkungan pemodelan Anda mendukungnya, gunakan skrip untuk menjalankan pemeriksaan validasi secara otomatis saat menyimpan.

- Pelatihan: Pastikan semua pemodel memahami perbedaan antara BDD dan IBD, serta aturan alokasi persyaratan.

- Dokumentasi: Pertahankan dokumen standar pemodelan. Gunakan dokumen tersebut saat memperkenalkan anggota tim baru.

Dengan menangani area-area khusus ini, Anda berpindah dari model yang rapuh yang rusak saat diperiksa menjadi aset yang kuat yang mendorong kepercayaan insinyur. Validasi bukanlah gerbang yang harus dilewati; ini adalah lingkaran umpan balik berkelanjutan yang memastikan model tetap menjadi representasi akurat dari sistem.

Fokus pada struktur, terapkan perilaku, hubungkan persyaratan, dan verifikasi batasan. Pendekatan disiplin ini mengurangi utang teknis dan memastikan implementasi MBSE Anda menghasilkan nilai dari konsep hingga pensiun.