Introdução ao Desafio da Integração 💡

A engenharia de sistemas é intrinsecamente complexa. Ao passar de modelos conceituais para hardware físico, a margem de erro encolhe significativamente. Uma das áreas mais críticas onde projetos frequentemente tropeçam é a rastreabilidade de requisitos. Este estudo de caso analisa um cenário do mundo real em que um esforço de integração de hardware falhou, não por falta de habilidade técnica, mas devido a uma falha na forma como os requisitos foram vinculados ao comportamento do sistema dentro de um framework de Linguagem de Modelagem de Sistemas (SysML). O objetivo é analisar os pontos de falha, compreender as implicações técnicas e demonstrar como um modelagem rigorosa pode prevenir resultados semelhantes.

A rastreabilidade é mais do que apenas um item na lista de verificação. É a base da integridade do sistema. Quando um requisito não está vinculado a um elemento de projeto, não há como verificar se esse elemento realmente atende à intenção. Em ambientes de alto risco, como no setor aeroespacial ou no desenvolvimento de veículos autônomos, essa desconexão pode levar a retrabalho custoso, atrasos no cronograma e riscos de segurança. Esta análise foca nos mecanismos da falha e nos construtos específicos do SysML que foram subutilizados ou aplicados incorretamente.

Contexto e Escopo do Projeto 📦

O projeto em questão envolveu o desenvolvimento de uma unidade de fusão de múltiplos sensores para uma plataforma de navegação autônoma. O sistema exigia a integração de LIDAR, radar e câmeras ópticas em um nó de processamento unificado. O ciclo de vida do desenvolvimento seguiu uma abordagem de Engenharia de Sistemas Baseada em Modelos (MBSE), utilizando SysML para definir a arquitetura e os requisitos.

Parâmetros Principais do Projeto:

- Tipo de Sistema:Conjunto de Sensores de Navegação Autônoma

- Fase de Desenvolvimento:Integração e Verificação do Sistema

- Tecnologia Principal:SysML para modelagem e especificação

- Resultado:Falha na integração devido a lacunas de requisitos não verificadas

A equipe criou um conjunto abrangente de requisitos durante as fases iniciais. No entanto, a ligação entre esses requisitos textuais e os blocos de design físico foi inconsistente. Embora a arquitetura inicial do sistema tenha sido modelada, a fase detalhada de integração carecia do rigor necessário nas cadeias de rastreabilidade. Essa desconexão só ficou evidente quando os primeiros protótipos físicos foram montados.

O Papel do SysML na Engenharia de Sistemas Moderna 🧩

O SysML fornece uma forma padronizada de descrever estruturas de sistemas, comportamentos e requisitos. Em um modelo bem estruturado, cada requisito deveria ser decomposto, alocado e verificado. A linguagem suporta vários tipos de diagramas, incluindo:

- Diagramas de Requisitos: Definem o “o quê” do sistema.

- Diagramas de Definição de Blocos (BDD): Definem a “estrutura” do sistema.

- Diagramas Internos de Blocos (IBD): Definem as “interfaces” e conexões entre blocos.

- Diagramas Paramétricos: Definem as “restrições” e relações matemáticas.

No cenário analisado, os Diagramas de Requisitos foram preenchidos extensivamente. A equipe conseguiu capturar com sucesso requisitos funcionais e não funcionais. No entanto, a alocação desses requisitos a blocos específicos nos BDD e IBD foi fraca. Muitos requisitos ficaram órfãos, ou seja, existiam no modelo, mas não tinham relações de saída para elementos de projeto. Isso criou uma falsa sensação de completude. O modelo parecia preenchido, mas o fluxo lógico de validação estava quebrado.

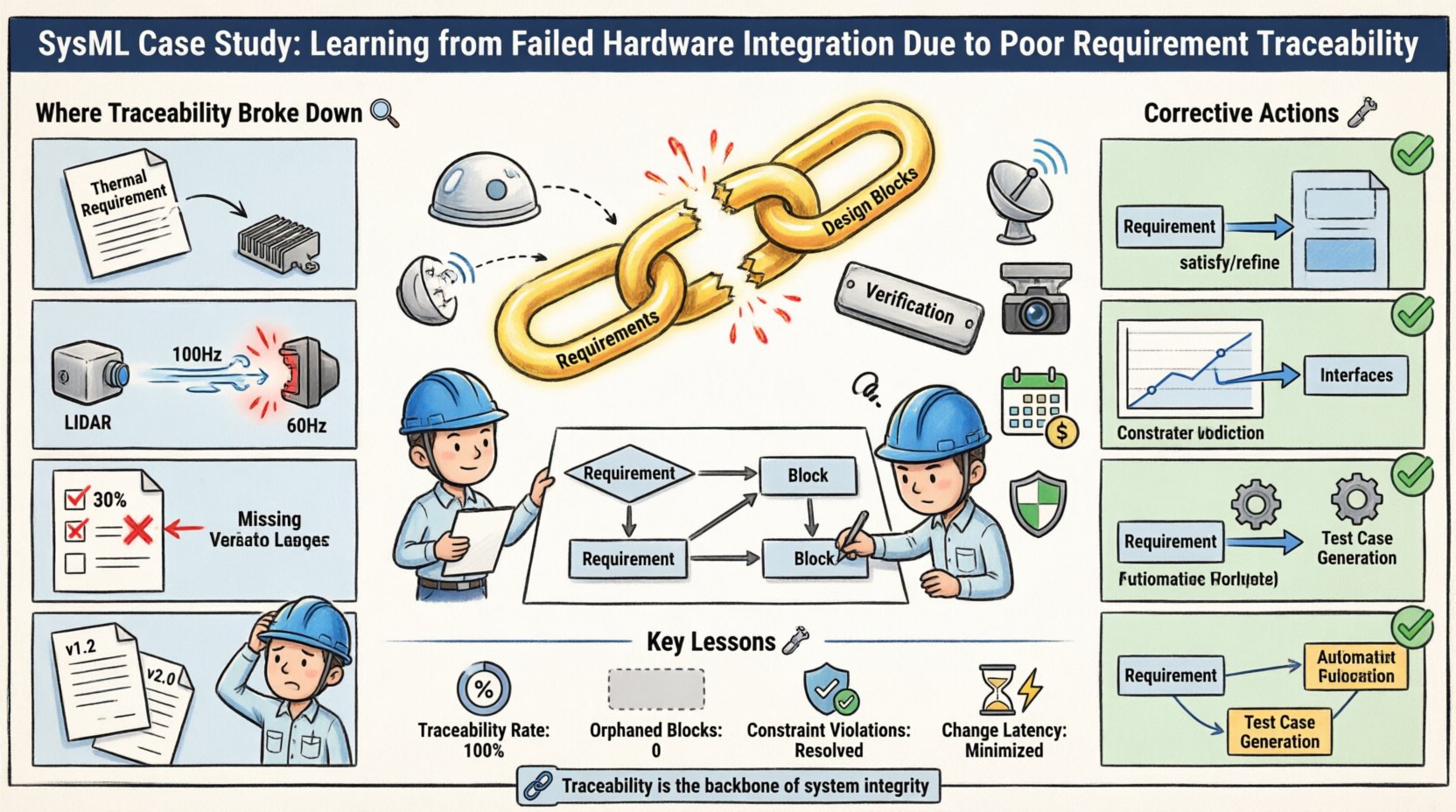

Onde a Rastreabilidade Falhou 🔍

A falha não foi um único evento, mas uma série de pequenos descuidos que se acumularam ao longo do tempo. Os pontos a seguir detalham onde as cadeias de rastreabilidade se romperam durante o processo de modelagem.

1. Alocação Inconsistente de Requisitos

Durante a fase de análise de requisitos, os engenheiros alocaram requisitos a blocos de sistema de alto nível. À medida que o projeto avançava para subsistemas, essas alocações não foram propagadas para baixo. Por exemplo, um requisito de gerenciamento térmico foi atribuído ao bloco “Unidade de Sensor” mas nunca foi vinculado ao componente específico “Dispositivo de Dispersão de Calor” no diagrama de blocos interno. Quando o hardware foi fabricado, o dissipador de calor estava subdimensionado porque o requisito térmico não estava ativamente influenciando as restrições de projeto.

2. Falhas na Definição de Interface

Diagramas de Blocos Internos definem as portas e conectores entre componentes. Neste caso, as interfaces de fluxo de dados foram modeladas, mas os requisitos de tempo de sinal não foram vinculados às portas de interface. A sequência de dados do LIDAR era esperada para operar a 100 Hz, mas o requisito que especificava essa frequência não foi associado à porta de interface de comunicação. Consequentemente, o controlador de interface foi projetado para 60 Hz, causando perda de dados durante a integração.

3. Vinculações de Verificação Ausentes

Um modelo robusto exige uma vinculação de verificação. Isso conecta um requisito a um caso de teste ou a um elemento de projeto específico que comprove que o requisito foi atendido. A equipe do projeto negligenciou criar essas vinculações de verificação para aproximadamente 30% dos requisitos. Sem essas vinculações, não havia forma automatizada de gerar um plano de verificação. A fase de testes tornou-se manual e improvisada, resultando em áreas de cobertura perdidas.

4. Controle de Versão e Desvio da Base

Os requisitos evoluíram ao longo do projeto. Foram feitos pedidos de alteração para acomodar novas tecnologias de sensores. No entanto, o modelo não impôs versionamento rigoroso nas relações entre requisitos e blocos. Quando um requisito mudou, os blocos de projeto upstream não foram sinalizados para revisão. Esse desvio significou que o hardware foi construído com base em uma versão mais antiga da especificação, que já não estava atualizada no modelo do sistema.

Comparação dos Estados de Modelagem 📊

Para visualizar a lacuna entre o estado pretendido e o estado real do modelo, considere a tabela de comparação a seguir. Isso destaca as áreas específicas onde a rastreabilidade foi insuficiente.

| Aspecto de Rastreabilidade | Estado Pretendido (Ideal) | Estado Real (Observado) | Problema Resultante |

|---|---|---|---|

| Alocação de Requisitos | 100% dos requisitos vinculados a blocos de projeto | 70% dos requisitos vinculados a blocos de projeto | Decisões de projeto não verificadas |

| Restrições de Interface | Tempo de sinal vinculado às propriedades da porta | Restrições de tempo apenas em texto | Incompatibilidade de interface (60 Hz vs 100 Hz) |

| Vinculações de Verificação | Vinculação direta a casos de teste | Matriz de rastreabilidade manual | Cobertura de teste perdida |

| Gestão de Mudanças | Análise automática de impacto em mudanças | Revisão manual necessária | Construções de hardware desatualizadas |

Análise Detalhada de Impacto 📉

As consequências de uma rastreabilidade inadequada foram imediatas e mensuráveis. A fase de integração, que estava programada para durar quatro semanas, se estendeu para doze semanas. A análise da causa raiz revelou que o hardware precisava ser reprojeto para atender aos requisitos originais que haviam sido esquecidos durante a fase de modelagem.

Implicações de Custos

A reprojetação da carcaça do sensor e da placa de interface de comunicação gerou custos significativos com materiais e mão de obra. A aquisição de novos componentes provocou aumentos de preço devido ao envio acelerado. O excesso orçamentário foi diretamente atribuído ao retrabalho necessário para corrigir os requisitos não vinculados.

Atrasos no Cronograma

Os testes de integração não puderam prosseguir até que o hardware correspondesse à especificação. O atraso adiou a fase de integração de software. Como o software dependia dos sinais do hardware, todo o cronograma de validação do sistema foi encurtado. Isso obrigou a equipe a trabalhar horas extras para cumprir o prazo de lançamento, aumentando o risco de introduzir novos erros.

Riscos de Segurança

O impacto mais crítico envolveu segurança. A falha na gestão térmica significava que os sensores poderiam superaquecer em condições de temperatura ambiente elevada. Isso não foi detectado durante os testes iniciais porque o requisito térmico não era monitorado ativamente no modelo. Em um ambiente de produção, isso poderia ter levado à falha do sistema durante a operação, representando risco para pessoas e bens.

Ações Corretivas e Melhorias no SysML 🛠️

Assim que a falha foi identificada, a equipe de engenharia implementou uma estratégia corretiva voltada para fortalecer as cadeias de rastreabilidade dentro do modelo SysML. Os seguintes passos foram tomados para restaurar a integridade na definição do sistema.

1. Regras de Alocação Forçadas

A equipe estabeleceu uma regra segundo a qual nenhum requisito poderia ser movido para a próxima fase de desenvolvimento sem uma alocação válida a um bloco de design. Isso foi imposto por meio de scripts de validação do modelo. Se um requisito não tivesse uma relação de saída ‘satisfazer’ ou ‘refinar’, o modelo o sinalizaria como incompleto. Isso obrigou os engenheiros a vincular cada requisito a um componente físico ou lógico.

2. Integração de Restrições de Interface

Os requisitos de tempo de sinal e taxa de dados foram transferidos dos documentos de texto para os diagramas paramétricos. Esses diagramas agora restringem explicitamente as propriedades das portas de interface. Isso garante que, se um requisito mudar, as restrições de interface se atualizem automaticamente, acionando uma notificação para a equipe de design.

3. Planejamento Automatizado de Verificação

A equipe implementou um fluxo de trabalho em que os links de verificação geram casos de teste automaticamente. Todo requisito com um link de verificação cria um item de teste pendente no sistema de gestão da qualidade. Isso garante que nenhum requisito seja verificado sem um plano de teste correspondente. Isso reduz o risco de erro manual na rastreabilidade da cobertura de testes.

4. Análise de Impacto de Mudanças

Quando um requisito foi modificado, o modelo foi consultado para encontrar todas as dependências downstream. Qualquer bloco que satisfizesse ou refinasse esse requisito foi destacado. Esse feedback visual permitiu à equipe identificar exatamente quais componentes de hardware precisavam ser reavaliados antes de implementar a mudança.

Lições para Projetos Futuros 🚀

Este estudo de caso oferece várias lições para equipes de engenharia de sistemas que adotam o MBSE. A lição principal é que o modelo só é tão bom quanto os links dentro dele. Um modelo cheio de elementos desconectados não oferece valor durante a integração.

- A rastreabilidade é um processo contínuo: Não é uma tarefa para ser concluída ao final de uma fase. A rastreabilidade deve ser mantida ao longo de todo o ciclo de vida à medida que os requisitos evoluem.

- Os links impulsionam o design: Os requisitos devem impulsionar a criação dos elementos de design, e não o contrário. Se um elemento de design existe sem um requisito, tecnicamente ele representa dívida técnica.

- A validação é essencial: Os links de verificação devem ser estabelecidos cedo. Esperar até que o hardware seja construído para verificar os requisitos é tarde demais.

- Suporte de Ferramentas: Embora ferramentas de software não tenham sido mencionadas especificamente, a capacidade de consultar relacionamentos e visualizar dependências é essencial. O rastreamento manual é propenso a erros.

Implementação de Cadeias de Rastreabilidade Robustas 🔗

Para evitar recorrência, a seguinte lista de verificação deve ser aplicada a todos os modelos SysML antes de passar para a fabricação de hardware.

Lista de Verificação Pré-Integração

- Cobertura de Requisitos:Todos os requisitos foram alocados a pelo menos um bloco?

- Completude da Interface:Todas as interfaces físicas têm tipos de dados e restrições de tempo definidos?

- Validação de Restrições:As restrições paramétricas são satisfeitas pelos valores atuais do projeto?

- Links de Verificação:Cada requisito possui um caminho para um caso de teste ou método de validação?

- Histórico de Alterações:A versão do modelo está sincronizada com a versão das especificações de hardware?

Métricas de Monitoramento

As equipes devem acompanhar métricas específicas para garantir a saúde da rastreabilidade. Essas métricas podem ser extraídas do repositório do modelo.

- Taxa de Rastreabilidade:Porcentagem de requisitos com links válidos.

- Blocos Órfãos:Número de blocos de design sem requisitos associados.

- Violações de Restrições:Número de restrições paramétricas que estão atualmente violadas.

- Latência de Alteração:Tempo decorrido entre uma alteração de requisito e a atualização do modelo.

Pensamentos Finais sobre Engenharia de Sistemas Baseada em Modelos 🏁

A falha descrita neste estudo de caso serve como um alerta claro sobre a importância da disciplina na engenharia de sistemas. O SysML é uma ferramenta poderosa que permite clareza e rigor, mas exige gestão ativa. A tecnologia não impõe automaticamente boas práticas; os engenheiros devem definir e aplicá-las.

Ao tratar o modelo como a única fonte de verdade e garantir que cada linha de código e cada componente em uma placa de circuito possa ser rastreado até um requisito específico, as organizações podem mitigar os riscos de falha na integração. O caminho para uma integração de hardware bem-sucedida é pavimentado com cadeias claras e ininterruptas de rastreabilidade. Quando essas cadeias são quebradas, o sistema físico sofre. Quando são fortes, o sistema é robusto, confiável e alinhado com sua intenção original.

Projetos futuros deveriam investir em treinamento e definição de processos em torno da rastreabilidade. Isso inclui definir o que constitui um link válido e estabelecer governança em torno das alterações no modelo. O custo da prevenção é sempre menor que o custo da correção. No contexto da integração de hardware complexa, a diferença entre sucesso e falha muitas vezes reside nos detalhes de como os requisitos são conectados dentro do modelo.